CMOS 反相器理论与仿真

CMOS 反相器理论与仿真

前言

了解 EDA 软体的发展历史的时候 EDA 軟體是怎麼發明的?從 Virtuoso 到 Verilog,看到了一张图

我突然就想读懂这张图及其背后的物理过程,将自己的心得记录下来。

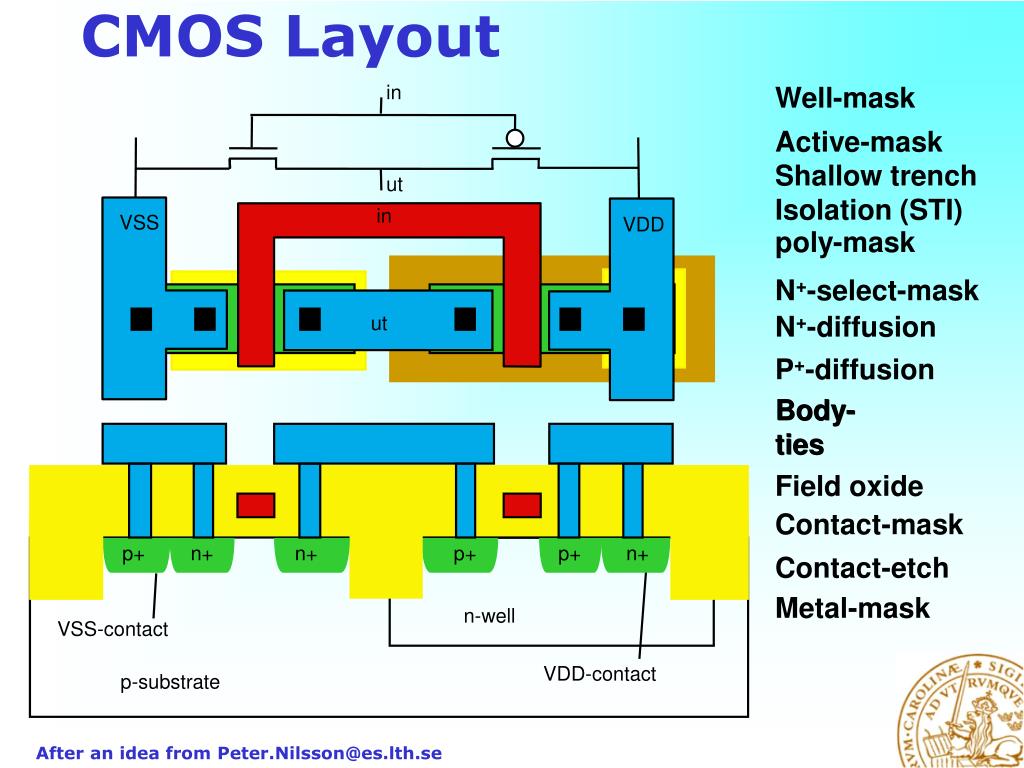

这是一张电路 Layout 的绘图,该图描述的器件是一个反相器。为什么这些红的蓝的绿的图案组合起来是一个反相器?内部的工作原理是怎样的呢?我挺感兴趣的!

CMOS 基础概述

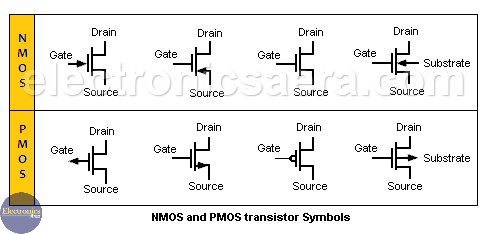

首先介绍一下 CMOS 的基础原理,想必我们在电路图中也经常看到下面这些器件

我们管将器件导通的载流子叫多数载流子,如果多数载流子为电子,则该 MOS 器件为 NMOS,如果是空穴,则为 PMOS。

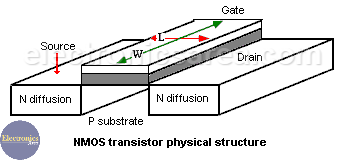

MOS 管相比BJT,除了栅极源极和漏极(对应 BJT 的基极发射极和集电极),还有一个体区。体区(通常称为衬底 Substrate 或 Bulk)是 MOSFET 结构的基础,通常连接到源极或一个特定的偏置电压,用于控制器件的阈值电压或提供静电保护。下面是 NMOS 管的物理结构

电路图中 MOS 器件符号中有个箭头符号,这个符号代表体区的 PN 指向。如果是 NMOS 管,体区是 P 掺杂,那么 PN 指向就是从体区指向栅极,箭头朝里。如果是 PMOS 管,体区是 N 掺杂,PN 从栅极指向体区,箭头朝外。

当对 NMOS 管的栅极加上了正电压,体区的电子会被拉拽到源极和漏极之间形成 N 型导电沟道,此时 NMOS 管就会导通产生电流。但如果是 PMOS 管栅极加上了正电压,作为多数载流子的空穴被排斥,导通电流所需的 P 型导电沟道更难产生了,PMOS 管就会关闭,由此实现了电流的开关功能。

MOS 管还分增强型和耗尽型,所谓的增强和耗尽,指的是零栅压下的管子的导通状态。增强型(Enhancement Mode)在栅源电压为零时是截止的,需要施加足够的正向(NMOS)或负向(PMOS)电压才能形成沟道并导通(增强载流子);而耗尽型(Depletion Mode)在栅源电压为零时已有沟道并导通,需要施加反向电压来“耗尽”沟道,使管子截止。增强型在数字电路中更常用,耗尽型可用于模拟电路中,且栅压可正可负。

反相器工作原理

CMOS 反相器由一只 PMOS 和一只 NMOS 构成,两者漏极相连作为输出,栅极共同作为输入。NMOS 源极接 VSS,PMOS 源极接 VDD。

- 当输入为高电平时,NMOS 导通、PMOS 截止,输出被 NMOS 拉到 VSS,得到低电平。

- 当输入为低电平时,PMOS 导通、NMOS 截止,输出被 PMOS 拉到 VDD,得到高电平。

因此该结构实现了输入逻辑的反相,故称“反相器”。

上图是反相器的俯视图和截面图,从截面图可以看出,左边是 NMOS,右边是 PMOS。当红色方块区域加上高电平时,左边 NMOS 形成 N 沟道并导通,输出被拉至 VSS 低电平;当红色方块区域加上低电平时,右边 PMOS 形成 P 沟道并导通,输出被拉至 VDD 高电平。这里之所以在 NMOS 左边有个 p+,在 PMOS 右边有个 n+,是因为 P-substrate(用于 NMOS)与 N-well(用于 PMOS)虽然分别为 P 型与 N 型材料,但它们都是轻掺杂区域,其体电阻非常高(kΩ 至 MΩ 级)。如此高的电阻无法保证 Body(体区)电位稳定地维持在 VSS/VDD。因此必须在体区中插入重掺杂的 P+ 或 N+ 区域作为 “Body Contact / Well Tie”,提供一个低阻路径,将 Body 牢固钳制到 VSS(对 NMOS)或 VDD(对 PMOS)。这样能够避免 Body 漂移、阈值变化和 latch-up 等问题。

我们回头来看这张图就很清晰明了了

左边是一个接地的 NMOS,p+ 和左边的 n+ 被遮住了;右边是一个 PMOS,刻意将 N-well 露了出来,还给最右边的 n+ 接了 VDD 以保证体区电压的稳定。

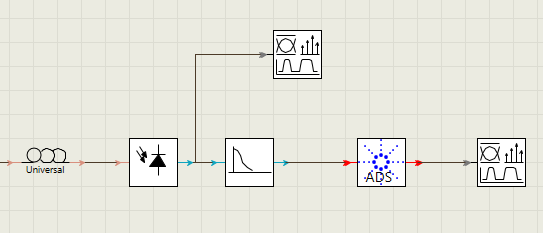

在 virtuoso 中仿真反相器

创建原理图

本来不想加这一栏的,但想了想,这也算是对 spectre 做一个简单的入门,毕竟前面刚入门了 SPICE。

想用 spectre 是有点麻烦的,原因在于这款 Spectre Circuit Simulator 已经和 Cadence 的 Virtuoso 集成在了一起,而后者作为 模拟/混合信号 IC 设计 的核心平台,软件相当笨重,有十几二十G。这还不算最有趣的,最有趣的是这款软件仅有 linux 平台的版本,安装起来配置各种环境和依赖相当棘手。因此我劝大家直接搞个虚拟机,装个镜像将就着用吧。毕竟咱们的目的是为了学习 spectre,而不是为了学习如何装这款软件…

在 linux 桌面直接点右键,打开 terminal 并输入 virtuoso 就能启动软件了。但此时你打开的只是一个日志界面,也就是初始界面。日志里会记录一些你的或 Virtuoso 的行为,例如文件加载,网表生成,错误警告等。

类似写程序脚本,我们第一次使用 Virtuoso,需要创建一个自己的工作区,在这里就是新建一个 library。

这里的 Technology File 代表工艺选择。也就是:这个库要不要知道金属层、via、DRC 规则、层定义、版图规则等?

| 选项 | 是否和 PDK 工艺关联? | 用途 |

|---|---|---|

| Do not need process information | ❌ 不关联工艺 | 不做版图,只做逻辑/仿真 |

| Attach to existing tech lib | ✔ 必须关联工艺(最常用) | 做 analog/mixed-signal 设计必须选 |

| Compile ASCII | 自己开发工艺库用 | 小众 |

| Reference existing | 共享已有 TechLib 层定义 | 较少使用 |

如果只做仿真,不需要 layout,可以不用关联 PDK 工艺。但如果需要 layout,就必须要关联工艺。因为你光有原理图没用,做出实物必须要画出版图,但版图不是你随便画的,有许多约束。

因此这里最好还是关联一个 PDK 的工艺,随便选一个就行。

有了 library,就可以在里面创建一个 cellview 了,这里选择原理图 schematic。

这里还可以选择 cell 的类型,例如 Spice,Spectre 等。

下面的 Open with 表示你可以用哪种应用打开,不同的 cell 格式需要用不同的应用打开,例如 Spice 就只能用文本编辑器打开。

|

|

|---|

绘制原理图

右键或者按键盘 I 就能开始往原理图上放器件。选定一个器件,按 Q 就能对属性进行编辑。添加端口按 P,旋转器件按 R。端口的输入情况后面仿真时会单独定义激励。此外,对器件的修改还可以在左下角的 Property Editor 中进行。导航栏 Navigator 可以按照类型,对器件,网络,引脚分类并快速定位。

|

|

|---|

仿真设置

原理图画好后就可以打开仿真应用了。这里用的是 ADE L(老版本的只做一次仿真,反正就走一下流程)。

在原理图界面左上角选项 Launch -> ADE L 打开仿真编辑器。

编辑激励 PORT,记住给 Enabled 打勾。

选择分析类型 tran,这个是瞬态分析,类似 SPICE 里的 .TRAN。

选定输出绘图,可以 From Design 对要输出的网络或端口进行选择,或者直接 to Be Plotted 选定要绘制的参数。

最后点击右侧的绿色小三角,开跑。得到的结果如图。

这里要注意的是,可以直接生成网表。如果仿真器选择的是 spectre,你导出的网表脚本就是 spectre 的脚本。

|

|

|---|

.scs 文件代表 Spectre Circuit Simulator,也就是生成的 spectre 的脚本送入到 spectre 仿真器中计算。这个语言很像我们前面入门讲过的 SPICE,因为 spectre 就是 SPICE 的加强版,语法更现代、结构更清晰、功能更强。