THE DESIGNER’S GUIDE TO SPICE AND SPECTRE

THE DESIGNER’S GUIDE TO SPICE AND SPECTRE

前言

前面对 DC 分析,瞬态分析和 AC 分析进行了比较详细的介绍,现在就能对 THE DESIGNER’S GUIDE TO SPICE AND SPECTRE 这本书进行快速概括与整合了。像我这种普通人也没很多时间对书本进行详阅,只需要提炼出最关键的内容和知识点即可,这大概也算我学过这本书了吧。

第一章:电路仿真

第一章不是教你怎么用仿真器,而是回答三个根本问题:

- 电路仿真是怎么发展到今天这一步的?

- 现代电路仿真器在算法层面到底在做什么?

- DC / AC / Transient 分析在数学与算法上有什么本质区别?

可以理解为给后面所有“MNA + 数值算法 + 收敛性问题”的章节打地基。

历史视角(Historical Perspective)

为什么需要电路仿真?

-

1970 年代 IC 复杂度急剧上升

-

实物原型:

- 成本高

- 调试困难

-

必须在流片前评估设计

两条技术主线

- IBM ASTAP:发展数值计算方法

- Berkeley SPICE:

- 成为事实上的工业标准

- 核心成功原因:

- 专门为集成电路建模

- 源码开放

- Berkeley 人才扩散到工业界

从 SPICE 到商业仿真器

- 70s–80s:

- IC 厂商 各自维护私有 SPICE

- 80s–90s:

- 商业仿真器性能、能力反超

- 内部自研仿真器逐渐消失

Spectre 的出现

- Berkeley → SPICE3

- Cadence → Spectre

- 核心思想:

- 不牺牲稳定性

- 用更好的数值算法提升速度

- 结果:

- 比传统 SPICE 快 3–5 倍

- 准确性与可靠性更高

- 核心思想:

算法视角(Algorithmic Perspective)

Direct Method(主流方法)

SPICE / Spectre 使用的传统路线:

- 写出电路的非线性微分方程

- 用数值积分(如梯形法)离散时间

- 每个时间点:

- 得到一组 非线性代数方程

- 用 Newton-Raphson

- 内部用 稀疏矩阵高斯消元

优点:稳定,通用,可靠

Explicit Integration(显式积分)——被否定的路线

- 如 Forward Euler

- 不解完整方程,只做外推

问题:

- 数值不稳定

- 时间常数稍小就会 blow-up

- 只在极少数数字 MOS 电路可用

Relaxation Methods(松弛法)

- 把电路拆成子电路

- 子电路交替求解

- 试图利用:

- 延迟(latency)

- 多时间尺度(multi-rate)

严重问题:

- 结果可能“看起来对,但实际上是错的”

- 类似没系安全带没刹车开车

作者态度非常明确,Relaxation 方法不值得信任

电路仿真三大分析类型

Transient Analysis(瞬态分析)

-

解的是:

-

方法:

- 时间离散

- 历史项参与计算

-

关键难点:

- 时间步长选择

- 误差会“沿时间累积”

DC Analysis(直流分析)

- 特例:

- 本质是 时间导数为 0 的瞬态问题

- 解法:

- Newton 迭代

- 风险:

- 不收敛 → 仿真失败

AC Analysis(交流小信号分析)

- 核心假设:

- 小信号 → 线性化

- 优点:

- 没有瞬态的数值稳定问题

- 没有 DC 的收敛问题

- 本质:

- 解线性方程组

- 用 LU / Gaussian elimination

方程建立的物理基础

Kirchhoff 定律

- KCL:节点电流和为 0

- KVL:回路电压和为 0

电路仿真不是“经验公式”,而是严格的物理守恒律

参考方向(Associated Reference Direction)

- 电压、电流方向必须统一约定

- “associated” 意味着正电流从 “+” 端流入,从 “–” 端流出

这是 MNA 正确 stamp 的前提

微分方程模型

- 元件模型 + 拓扑连接

- 自动构造一组 ODE

- 现代仿真器基于 Modified Nodal Analysis (MNA)

电路仿真 = 基于物理守恒律的方程建模 + 稳定可靠的数值算法,而 SPICE / Spectre 的所有设计选择,本质上都是在“准确性、稳定性、效率”之间取最安全的平衡。

从物理定律到节点方程

把“电路”系统性地写成一组微分方程,并说明不同分析(DC / AC / Transient)只是对同一组方程的不同处理方式。

节点分析的统一形式:

它的含义非常深刻:

| 项 | 物理意义 |

|---|---|

| 由电阻等瞬时元件产生的电流 | |

| 由**储能元件(电容/电感)**引入的动态项 | |

| 独立源注入的电流 | |

| = 0 | KCL 在节点层面的直接表达 |

非线性元件的引入

节点方程仍然成立

但:

- 是指数非线性

- 电容可能也是电压相关的非线性电容

非线性器件的建模本质

半导体器件 = 非线性电阻 + 非线性电容

三种分析在同一方程下的区别

Transient Analysis(瞬态)

-

解的是:

-

特点:

- 有时间

- 有历史

- 误差可能积累

-

输入:

- 激励波形

- 初始条件

最通用、最难、计算量最大

DC Analysis(直流)

通过假设:

方程退化为:

本质:

- Transient 的“时间冻结版本”

- 解的是 平衡点

- 仍然是 非线性代数方程

- Newton 迭代

AC Analysis(小信号)

- 在 DC 工作点附近线性化

- 假设激励很小

- 目标:

- 稳态正弦响应

- 传递函数

AC 分析 既没有 transient 的数值稳定问题,也没有 DC 的收敛问题

建模:为什么仿真器“好坏”差别巨大

模型质量 = 仿真质量

准确性、收敛性、效率都需要考虑在内

Spectre 比 SPICE更快、更稳,很大程度来自模型实现得更谨慎

两类模型来源

| 来源 | 例子 |

|---|---|

| 内建模型 | SPICE 的二极管 / MOS |

| 用户模型 | Verilog-A / SpectreHDL |

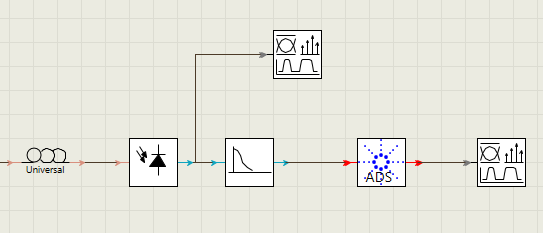

行为级建模(Behavioral Modeling)

- 系统级

- 顶层 / 底层协同

- 激励、测量、电路块抽象

第二章:直流分析(DC Analysis)

第二章主要讲的是:“直流工作点/平衡点(DC operating point / equilibrium point)到底在算什么、为什么难收敛、收敛判据怎么定、工程上怎么排查/提高收敛与精度、以及 DC 分析在实际电路里会遇到的典型问题(多解、大电路、重启)”

引言:为什么 DC 分析重要、难点是什么

- 直流工作点是很多分析的基础:

.op/.dc/.ac/.noise以及瞬态初始点都依赖“能否可靠求出 operating point”。 - 基本思想:把独立源固定成常值;电容在 DC 下等效开路、电感等效短路;然后解得到一组非线性代数方程。

- 关键现实:非线性方程只能用迭代(如牛顿法),但并不保证总能成功;因此 DC 分析的核心痛点是收敛(精度通常是次要的,收敛了往往不至于太离谱)。

理论:DC 方程、牛顿法、收敛判据、收敛为何失败

DC 解的性质:可能不唯一、还可能不稳定

- 明确强调两点:

- 电路可能有多个 DC 解;

- 仿真器算到的 DC 解不一定稳定(可能是不稳定平衡点)。

求解非线性方程:Newton–Raphson(牛顿法)

-

DC 方程(以及瞬态每一步)都是非线性代数系统,通常用 Newton-Raphson:从初值开始,线性化电路 -> 解线性方程 -> 更新 -> 重复,直到满足收敛条件。

-

给出了标准形式:迭代中用 Jacobian(雅可比矩阵)把非线性问题变成一串线性问题;并指出“理论上要在足够近的初值附近才保证收敛”,而电路仿真里这些条件不总成立,所以“不收敛”是设计师最常抱怨的问题之一。

书中的雅可比矩阵(Jacobian)是“非线性电路在当前工作点的线性化斜率矩阵”,它不是几何意义上的斜率,而是 KCL 残差对未知量的偏导数矩阵。雅可比矩阵奇异,指的是该雅可比矩阵非满秩,存在未被约束的自由度,也就是方程数量不够无法求解所有的未知量。

收敛判据:为什么要两类(残差 + 更新量)

- Spectre 使用的判据核心思想是:

- 残差/节点 KCL 误差()要足够小(保证 KCL 近似满足);

- 迭代更新量()也要足够小(限制解的误差/漂移)。

- 并解释了两者各自“更关键”的场景:

- 低阻/强非线性节点(比如强正向偏置结),残差判据更重要;

- 高阻/近似隔离节点(比如反偏结隔离的节点),更新量判据更重要。

- 实用上会用“相对+绝对容差”的形式,比如

reltol、vntol(vabstol)、abstol(iabstol)来适配不同信号尺度,避免小信号被迫收敛到超过数值舍入误差的程度。

收敛问题本质:大多不是算法“没用”,而是起点/电路/参数导致

- 书中给了一个非常“工程”的观察:很多收敛问题来自连线/参数/模型参数不合理;仿真器会提供拓扑检查来提前发现一部分问题,但如果仍不收敛,就要回头认真查 netlist 的拓扑与参数合理性。

收敛增强:Continuation / Homotopy(续接法)

书里把“让牛顿法更容易收敛”的办法归到 continuation/homotopy:先解一个“更容易的电路”,再逐步变回原电路。

- 常见三种:source stepping、gmin stepping、pseudo-transient;Spectre 三种都有,并额外提供 damped pseudo-transient(dptran),更容易收敛。

- gmin stepping:给所有非线性器件并联小电导/电阻,让电路先“更线性、更不容易漂”,然后逐步减弱/移除它们直至原电路。

- source stepping:把所有源从 0 慢慢 ramp 到目标值,每一步都重新求解并把上一步当初值。

- 它们可能失败的典型原因:解曲线上的不连续、fold(折返,多解)、bifurcation(分岔,对称电路常见);并给了经验:source-stepping 往往比 gmin-stepping 更容易被 fold/分岔困扰;对称电路可以用非对称 nodeset来避免分岔。

- pseudo-transient:给每个非线性器件并一个“伪电容”,把 continuation 参数当成“伪时间”从 0 sweep 到 ∞ 去找 DC 解;但如果加了这些电容反而让电路变成振荡器,会失败。

实战:不收敛怎么办、精度不够怎么办

收敛问题排查/处理清单

书里给了“建议列表”,例如:

- 先看仿真器 warning/error;在 Spectre 里可开

diagnose=yes获取更多定位信息。 - 检查参数是否合理(Spectre 有

+param等机制帮你做合理性检查)。 - 检查连线/节点信息(Spectre 可用

info what=nodes/terminals)。 - 处理小的“浮置电阻”等导致的数值问题;必要时调整

iabstol;检查电流源方向,避免“强迫电流倒灌二极管/结”等导致困难;给更多 nodeset;开启 continuation;提高迭代上限;必要时调整gmin(但要警惕会影响电路行为)。

DC 精度:容差与 gmin 的双刃剑

- 书里强调:收敛判据允许一定 KCL 误差(可类比为在每个节点接了很小的电流源);这对高阻节点会造成明显电压误差,所以需要配合“更新量判据”限制电压误差。

reltol=0.1%不代表结果就有 0.1% 精度(因为更新量比较的是相邻迭代,不是与真解直接比较)。gmin:太大影响精度,太小影响收敛;如果gmin大到能显著改善收敛,通常也已经大到会影响精度/电路行为,需要谨慎。

精度问题怎么处理

- 总原则:想更准就收紧

reltol,并确认abstol/vntol合理;但有时收紧太多会拖慢或也未必解决本质问题。 - 书里还给了“先假设:仿真器算的是‘错误电路的正确解’”,用工作点去反推检查拓扑/参数/模型/电源;考虑多解的可能,用 nodeset 引导到你想要的解;确认

gmin没在“改电路”,必要时尝试设为 0(但可能带来奇异 Jacobian)。

DC 分析的典型应用与“坑”

- 本章最后一大段讨论 DC 分析里会遇到的电路现象:从“多工作点电路”举例讲起(例如电流基准/镜像类电路的交点决定工作点),然后讨论大电路如何更稳健地求解,以及如何从已有解重启以加速后续分析。

小结

- DC 工作点=求平衡点(源常值、电容开路、电感短路) -> 得到非线性代数方程。

- 主要靠牛顿法,但收敛高度依赖初值/电路“是否隔离解”/模型连续可导等条件;因此需要合适的收敛判据与工程技巧。

- 工程上:先查警告与拓扑/参数,再用 nodeset、迭代上限、

gmin、continuation/homotopy(source stepping/gmin stepping/pseudo-transient/dptran)等手段“把牛顿法带到正确的盆地”。

第三章:交流分析(AC Analyses)

这一章主要在讲交流分析到底在算什么、它的数学前提是什么、能算什么、不能算什么、以及工程上如何正确使用和解读 AC 分析结果。

引言:AC 分析是什么,不是什么

AC Analyses 是“一族频域分析”

书里明确说,AC Analyses 不是单一分析,而是一整类方法,包括:

- AC analysis(小信号频率响应)

- Transfer Function (XF) analysis

- Scattering parameter (SP, TDR) analyses

- Noise analysis

它们全部基于同一数学基础:Phasor analysis(相量分析)

AC 分析的统一前提

AC 分析必须同时满足:

- 电路已经有 DC 工作点

- 在 DC 工作点附近进行线性化

- 激励是小信号正弦

因此,AC 分析看不到:

- 失真

- 频率搬移

- 混频

- 非线性效应

AC 分析只能反映线性化后电路的行为

理论:AC 分析在数学上到底做了什么

从时域到频域:相量法

-

假设所有信号都是:

-

微分算子:

于是:

- 电容:

- 电感:

这一步直接“消灭了时间” -> AC 分析不再是微分方程,而是线性代数方程。

AC 分析本质

-

非线性器件 -> 小信号模型

-

得到并求解

每个频点都是一次独立的线性求解

实战:不同 AC 分析的具体内容

AC(小信号频率扫描)

- 最常用

- 给一个 AC 幅度源,扫频,得到:

- 幅频

- 相频

- 传递函数

注意:幅值本身没有物理意义,比例关系才有意义

Transfer Function(XF)分析

XF 分析直接计算:

- 输出对输入的增益

- 输入阻抗

- 输出阻抗

这是 AC 分析的“解析形式”版本,避免后处理出错。

S-Parameter / SP / TDR 分析

书中特别强调:

- Spectre 可以直接在频域算 S 参数

- 不需要先 transient,再 FFT

SP 分析的本质仍然是:

- 线性化

- 频域求解

噪声分析(Noise Analysis)

噪声分析的基本假设:

- 随机

- 高斯

- 小信号

因此:

- 仍然适用线性化电路

- 用 叠加原理

要噪声源模型

-

电阻(热噪声 / Johnson-Nyquist)

-

半导体结(Shot noise)

-

与直流电流有关

-

表现为并联噪声电流源

-

-

Flicker Noise(1/f 噪声)

-

低频主导

-

MOS / 电阻中常见

-

所有噪声最终都被等效为:

- 电压噪声源

- 或电流噪声源

噪声分析算的是噪声的谱密度

应用:AC 分析的应用实例

这里讲了半天的运放反馈系统,好像跟 AC 无关,但实际上运放反馈是 AC 分析“最容易被误用、但又最有工程价值”的场景。真正要解决的不是“运放”,而是这 3 个问题:

AC 分析算出来的“增益”,到底是哪一种增益?

- 闭环增益?

- 开环增益?

- 环路增益?

在不破坏 DC 工作点的前提下,怎么用 AC 得到“系统级量”?

- 稳定性

- 相位裕度

- 环路增益

- 输入/输出阻抗

当电路不再是“理想单向块”时,AC 结果还可信么?

- 双向耦合

- 加载效应

- 反向传输

为什么“反馈运放”是最佳示例?

因为它同时具备:

| 特性 | 对 AC 分析的挑战 |

|---|---|

| 强反馈 | 极点/零点/稳定性全靠 AC |

| 多种“增益”概念 | 最容易混 |

| 经常被“断环测” | 最容易用错方法 |

| 非理想效应明显 | 单向假设最容易失效 |

运放反馈的表征

理想运放原理图

由于开环增益有限而非无穷大,这里不宜使用虚短的概念(虚断还是要用的)。

所谓虚短,指的是运放正端负端电压一致,虚断,指的是运放正端负端输入电流近似为零。这种假设在如下 shunt-shunt 型反馈系统中是合理的,因为无穷大开环增益对应输入差分电压必须为零,否则输出无穷大。此外若输入端存在电流,由于正负端存在输入阻抗,也会导致等效差分电压不为零,输出无穷大。如果你问输入阻抗为零,即便存在电流,差分电压也为零难道不行么?也不行,因为这样会导致运放输入端被短路,运放不工作。

计算公式

下面只使用虚断,是因为要确定 的负载点电压只与反馈支路有关,与运放内部无关。

根据上述示意图,反馈电压 ,反馈系数 ,则 。

令开环增益为 ,闭环增益为 ,开环增益输出 ,

令环路增益为 ,

因此,用来表征反馈系统的四个重要参数为:

运放的结构

根据输入或输出信号的类型(电压或电流),区分的四种配置。电压为串联,电流为并联。

针对不同的配置,四个增益参数的定义也分为电压比电压,电压比电流,电流比电压和电流比电流。

串联——并联结构最好理解(前面表征里的图就是),并联——并联也好理解,因为电压源串联反馈电阻相当于电流源并联反馈电阻。不好理解的是输出端,如何理解输出电流表现为运放与反馈系统的串联?下面给出一张典型的 series-series 结构

这里将该电路的解释浓缩成精华

-

之所以存在电阻 ,是为了拉低 下端的节点电平,这样可以提高负载 的输出电压

-

之所以存在 和 ,是因为可以通过分压的方式调整运放负端的输入电平

-

整个反馈系统是由 , 和 共同组成

-

输出端本质还是电压并联,从 接出一个端子就是 ,左边是运放,右边经过 后进入反馈系统,运放与反馈系统呈并联结构

-

但是对电流输出端来说,运放与反馈系统呈串联结构

-

整个运放可以等效为一个局部线性化器件,它包括:

-

输入端(差分端口)

- 正端:

- 负端:

- 两端之间存在一个差分输入电阻

也就是说:

-

受控源(核心放大机制)

在运放内部,有一个受控电压源(VCVS):

- 控制量:差分输入电压

- 放大倍数:开环电压增益

-

输出端(非理想输出)

- 在受控源之后,串联一个输出内阻

- 外部看到的运放输出电压是:

或等效为“受控源 + 串联电阻”的 Thevenin 等效输出

-

闭环后放大倍数改变的根本原因,是负反馈迫使差分输入电压趋近于零,使系统的传递关系由外部反馈网络主导;差分阻抗和输出内阻只是通过分压对结果做有限修正,而不是主因。

-

反馈系统的测量

核心来了,教学上说,环路增益是环路断开时的增益,这是因为环路闭合时,你无法单独看到 和 ,它们是会随着环路次数迭代耦合的。因此需要将环路断开后,从断点注入,绕一圈回到断点,则得到的增益正好是

在这个特殊前提下:“断环测到的增益 = 环路增益”

但是,这句话隐含了一个没说出口的前提:断环不会改变环路本身的特性

而这在真实电路里几乎从不成立。

具体来说,断环会:

- 改变负载条件

- 改变各级的工作点(哪怕 DC 保持)

- 改变小信号耦合关系

- 改变 Jacobian

系统已经不是原来的反馈系统了,测到的“增益”,还能叫原系统的环路增益吗?

真正的环路增益是:

在原系统保持不变的前提下,一个微小扰动沿反馈路径传播一圈后,回到起点的比例因子。

AC 分析测量环路增益

作者到目前一直都在回答一个非常核心的问题:

AC 分析只能解线性化的小信号方程,那我到底该如何用 AC 分析,才能在 不改变系统 的前提下,测到我真正关心的“环路增益”?

先“否定”三种直觉做法(a 是待测结构):

- b 直接断环

- c 使用 LC 低通:DC 闭环,AC 开环

- d 用 AC/DC 行为不同的电阻或开关

这三种测量运放环路增益的方法都存在问题,即

-

改了拓扑

-

改了 Jacobian

-

算的已经不是原系统的小信号模型

另外 AC 激励放在哪个端口也很重要,因为端口的其他信号可能会污染你要测的量。

运放的目的是放大差模信号,但运放除了差模增益 ,也有共模增益 。

给个例子,在运放正端和负端分别施加激励

假定差模增益 ,共模增益 ,反馈系数 。

如果在运放正端施加激励(a)

计算得到的开环增益为

这个跟我们真正想求得的 完全不一样。造成这种现象的原因在于,通过将激励放置于运放正端,会导致共模增益污染我们想求得的结果。

如果将激励施加于运放负端(b)

此时测到的 几乎就和 几乎一致了

总结上述三种测量环路增益的错误做法

-

Breaking the Loop(直接断环)

- 会扰乱 DC 工作点

- 高增益系统下:

- 一个很小的 DC 偏移

- 输出就会打到 rail

AC 分析前提是:线性化围绕某个 DC 点,你把 DC 点毁了,AC 结果就没有物理意义

-

Using a Low-Pass Filter(LC 法)

问题有三层:

- 频带选不好 -> 干扰测量

- L/C 极大 -> 数值病态

- L/C 本身 -> 改变了环路特性

-

Opening the Loop Only During AC

这是三者里最好的一个,但作者仍然不满意:

- DC 点是对的

- 但 AC 时加载条件变了,高频尤其不准

测量环路增益的正确方法是:Middlebrook’s Method

不改变系统结构,只是在环路里“注入一个小信号扰动”,用 AC 分析看它绕环一圈后的响应。

各种测量方法的能力极限

上面各种 AC 分析去测量一个运放在反馈系统中的环路增益,都是存在极限的,它们在高频下都会逐渐偏移参考值(反馈因子在高频下也会偏离参考值)。

这里 G-parameter 不是一种“工程测量技巧”,而是在“整个反馈系统不被破坏”的前提下,对反馈参数所做的严格、系统级定义;它给出的结果被作者当作“参考真值(reference)”,用来衡量前面那些工程测量方法在高频下偏离了多少。

也就是说,所谓的 G-parameter 可以通过对“整个反馈网络”做 AC 仿真,在选定的端口上直接计算得到;它得到的增益谱反映的是该反馈系统在实际工作点下、线性化后的“真实系统级增益谱”,而不是通过断环、注入等工程手段“测”出来的近似结果。

书中比较了四类测量环路增益的方法:

- 闭环法(closed-loop) —— 最差,仅在极低频勉强有意义

- 断环类方法 —— 包括

- 直接断环

- LC 低通

- AC-switch

- Middlebrook 方法 —— 不断环的工程可用方法

- G-parameter 方法 —— 非理想电路的参考标准

通过对比可以看到,不论哪种工程方法,在高频时都不够准确,这是因为在实际的反馈电路中,电容和电感的负载效应通常对其行为起着重要作用。此外,反馈网络几乎都不是单向的,通过反馈网络的前向耦合会通过增加右半平面零点(增益曲线零点,即放大倍率为1时的许多个频率点)而强烈影响稳定性。

高频失效的原因在于,反馈网络在高频下对运放产生显著加载并引入双向耦合,使得输出扰动可通过非理想反向通道直接影响输入,从而绕过理想的前向放大路径。通过用理想受控源替换反馈网络,可以隔离这些加载与反向耦合效应,从而测量运放本身的开环小信号特性。

注:这里说的“加载(loading)”,指的是:运放与反馈网络在小信号下形成的整体,对输入端与输出端产生的双向电气耦合与约束,而不是“某个电阻拉低了某个节点”这种狭义加载。

当使用受控源替换反馈网络后,也就是只要把“加载”这个因素消掉,AC 分析是完全能给出准确开环增益的。

在测量电路的反馈参数时,重要的是要认识到,除非各个元件都是理想的,否则不应仅根据对各个元件的测量来得出结论。

有效开环增益取决于源、负载和反馈电路。同样,有效反馈系数取决于放大器。要准确测量反馈参数,必须将电路作为一个整体来运行。特别是那种认为应断开反馈环路来测量环路增益的观点,只适用于理想电路。这意味着在实际操作中,几乎不应断开反馈环路。即使是包含运算放大器的电路,也应在仿真时保持反馈环路完整,因为在高频下,负载效应和双向耦合的影响是显著的。

当放大器“不是电压放大器”时,问题更严重,这里换成 反相 / shunt–shunt 配置

-

输入是电流,输出是电压,运放本质是 跨阻放大器

-

用电阻做反馈 -> 输入被严重加载 -> 测到的“开环跨阻”被压扁

-

用理想电流源反馈 -> 不加载 -> 跨阻巨大(隔绝了负载效应和双向耦合,运放给出完全不一样的增益效果)

真实电路里,“放大器”和“反馈网络”不是独立存在的实体,强行把它们分开分析,本身就是错误建模。

总结所有 AC 分析的测量方法,作者给出了结论:

不要 先验地 给整体电路施加块边界,再用 AC 去“验证”这些块;而应该让 AC 分析揭示系统的真实行为,再据此 事后 识别哪些等效块是合理的。

在 AC 分析里,真正可靠的对象不是“你以为的模块”,而是“线性化后整个电路的实际行为”。

反馈网络的 Y 参数表示法

Y-parameter 对应并联——并联反馈网络

所谓的 Y 参数就是导纳参数矩阵,反馈网络中的运放和反馈系统是根据诺顿等效为理想电流源和并联电阻,并且认为不论是运放还是反馈系统,都看成是一对控制与受控电流源。

为什么用导纳矩阵,是因为 shunt–shunt 的端口行为天然是“诺顿型(电流源 + 并联)”

因此,将该模型中各导纳与电流源合并,得到等效网络模型(导纳矩阵)

考虑到 , 与这些矩阵元之间的关系

闭环增益为

这里的 是开环增益, 是反馈系数,因此

shunt-shunt 测量 Y/Z 参数的方法

在真实反馈电路中,应通过 AC 分析测量二端口的 Z 或 Y 参数(只在 AC 时注入测试源),再通过严格的网络参数换算,得到系统级反馈参数;这一过程避免了先验分块,也自动包含加载与双向耦合效应。

书中的测量电路

用于测量并联并联反馈电路的 Y 参数和 Z 参数的测试电路。测量 Y 参数所需的电压源仅在交流分析期间连接到电路中,以防止它们干扰运算放大器的工作点。在正常运行时,开关处于打开状态。要测量 Y 参数,需闭合开关并进行两次交流分析,一次是 且 ,另一次是 且 。要测量 Z 参数,需打开开关并进行两次交流分析,第一次是 且 ,第二次是 且 。

注意到一个奇怪的点:为什么前面四种反馈结构,shunt-shunt 画的是输入电流(并联)输出电压(并联),而现在 shunt-shunt 测量的却是导纳矩阵,即输入电压测量电流?

这是因为前面描述反馈结构时,说的是这个反馈结构在系统意义上控制的物理量类型,即系统抽象上看待放大部分与反馈部分的连接关系。如果 shunt-shunt,则输入端需要电流分流才能实现反馈;输出端需要将电压直接送入反馈网络。但具体实现上用什么端口变量来表征这个系统的线性二端口关系,是由测试员决定的,与前面的系统抽象表述不在一个层级上。系统抽象上实现电流分流不一定只能用电流源,用电流源戴维南等效后的电压源一样可行!

AC 分析之所以需要“单独加激励”,正是因为 AC 解的是“在 DC 工作点附近的线性化系统”,这个激励必须只进入线性化后的系统,而不能改变原电路的 DC 拓扑与工作点。

对任意二端口网络 :

含义是:

实际操作流程(Y 参数)

测 Y 参数需要 两次 AC 分析:

测 :

- 设:

- 测:

测 :

- 设:

- 测:

为什么作者转而推荐 Z 参数?

Z 参数定义

- 电流是激励

- 电压是响应

Z 参数更“工程友好”,原因有三个:

- 电流源不容易破坏 DC 工作点

- shunt–shunt 本来就是“电流输入 -> 电压输出”

- 数值稳定性更好

实际测量流程(Z 参数)

测 :

- 设:

- 测:

测 :

- 设:

- 测:

Z -> Y 换算公式

书里用的是标准网络理论:

结合 Y 参数表示法中的 ,,, 公式

这里需要提一句,不管你测的什么矩阵(YZHG 矩阵),目的都是为了计算上面 ,,, 参数。

反馈网路的 Z 参数表示法

Z-parameter 对应串联——串联反馈网络

所谓的 Y 参数就是阻抗参数矩阵,反馈网络中的运放和反馈系统是根据戴维南等效为理想电压源和串联电阻,并且认为不论是运放还是反馈系统,都看成是一对控制与受控电压源。

为什么用阻抗矩阵,是因为 series–series 的端口行为天然是“戴维南型(电压源 + 串联)”

因此,将该模型中各导纳与电流源合并,得到等效网络模型(阻抗矩阵)

考虑到 , 与这些矩阵元之间的关系

闭环增益为

series-series 测量 Y/Z 参数的方法

从整体二端口关系出发

这里的视角已经变了:

- 输入是 电流

- 输出是 电压

因为 series-series 端口行为是串接,在端口串电流源测试会破坏环路/工作点(强行规定电流,KVL/反馈关系就被破坏),因此这里要用电压源激励、测电流,从而得到导纳(Y)参数

-

第一次 AC,得到

-

设:

-

AC 求解后读出端口电流

-

因为此时 :

-

-

第两次 AC,得到

-

设:

-

读出

-

因为此时 :

-

再从导纳矩阵反推阻抗矩阵

结合 Z 参数表示法中的 ,,, 公式

总结一下前面的 shunt-shunt / series-series,虽然等效模型中是算的输入电压经过导纳矩阵得到输出电流 / 输入电流经过阻抗矩阵得到输出电压,但为了保证端口测试不破坏 DC 工作点,都采取了测另一种对应的矩阵,再换算回原矩阵的方法。

- shunt-shunt 的 DC 工作点是电压确定的,这是因为 DC 电压同时加载在运放与反馈网络。加电压激励如果不在 DC 工作点,会导致 AC 分析前的 DC 分析与后续激励的 DC 不一致,产生错误。

- series-series 的 DC 工作点是电流确定的,这是因为 DC 电流同时流过串联的运放与反馈网络。加电流激励如果不在 DC 电流工作点,会导致 AC 分析前电流 DC 分析与后续激励的 DC 不一致,产生错误。

反馈网络的 H 和 G 参数表示法

H-parameter 对应串联——并联反馈网络;

G-parameter 对应并联——串联反馈网络。

在系统级上,输入串联对应电压分压控制运放输入,输出并联对应输出电压反馈至反馈网络,因此输入端应用戴维南等效,输出端应用诺顿等效。

因此,将该模型中各导纳与电流源合并,阻抗与电压源合并得到等效网络模型(传递矩阵)

对应 ,,, 公式

在系统级上,输入并联对应电流分流控制运放输入,输出串联对应输出电流反馈至反馈网络,因此输入端应用诺顿等效,输出端应用戴维南等效。

等效网络模型(传递矩阵)

对应 ,,, 公式

series-shunt 与 shunt-series 测量 H/G 参数的方法

从整体二端口关系出发,series-shunt 有

shunt-series 有

测量 H/G 参数的电路示意图如下

测量 H 参数

想要测量 H 参数,需要输入并接电压源,输出串接电流源,这样就会影响 DC 工作点。因此实际操作是在输入串接一个电压激励,测输出电流,得到 G 矩阵再根据公式换算成 H 参数。首先关闭输入开关,打开输出开关,并设

-

-

( 断路)

-

AC 求解后读出端口 ( 的电流)( 的电压,也就是 两端电压)

-

此时:

-

-

-

( 短路)

-

AC 求解后读出端口 ( 的电流)( 的电压)

-

此时:

-

再根据公式换算

测量 G 参数

同样的,测量 G 参数,系统层级上属于 shunt-series,作为二端口网络,输入电流,输出电压。直接测量的话需要输入串接电流源,输出并接一个负载测电压。但这样的话 AC 激励的 DC 工作点可能与 AC 前的 DC 不一致(AC 前一定会做 DC 分析,确定工作点,然后 AC 小信号近似分析),因此只能间接测量,通过输入端串接一个电流源,测量 H 矩阵再根据公式换算成 G 参数。首先打开输入开关,关闭输出开关,并设

-

-

( 短路)

-

AC 求解后读出端口 ( 两端的电压),( 两端的电压)

-

此时:

-

-

-

( 断路)

-

AC 求解后读出端口 ( 两端的电压),( 两端的电压)

-

此时:

-

再根据公式换算

四种反馈结构总结表

逻辑关系递进

-

series-series 的系统关系是 V <-> I,它的等效电路两边均为戴维南等效 ,因此二端口矩阵为阻抗矩阵Z。Z矩阵满足的关系为

-

shunt-shunt 的系统关系是 I <-> V,它的等效电路两边均为诺顿等效 ,因此二端口矩阵为导纳矩阵Y。Y矩阵满足的关系为

-

series-shunt 的系统关系是 V <-> V,它的等效电路输入端为戴维南等效 ,输出端为诺顿等效 因此二端口矩阵为阻抗和导纳的混合矩阵H。H矩阵满足的关系为

-

shunt-series 的系统关系是 I <-> I,它的等效电路输入端为诺顿等效 ,输出端为戴维南等效 ,因此二端口矩阵为阻抗和导纳的混合矩阵G。G矩阵满足的关系为

传递函数随偏置的变化

小信号增益不是常数,而是 DC 偏置点的函数。AC 分析不只可以扫频率,还可以“扫偏置”,从而研究线性区到底有多大。

- SPICE:只能扫频率

- Spectre:可以扫

- 频率

- 温度

- 元件参数

- 偏置

这是 Spectre 相对 SPICE 的一个能力扩展

对一个简单的差分对进行 AC 分析,研究其跨导随 DC 偏置点的变化,可以看到简单差分对线性区非常小

用 AC 小信号分析 + 偏置扫描,提取“非线性器件的等效电容/电导”。

例如

-

对二极管施加:

- DC 偏置

- 一个 单位幅度 AC 电压

-

测小信号电流

-

得到导纳:

然后分解:

于是:

需要注意的是:

- 寄生电阻会污染测量,测到的不是“本征结电容”

- BJT 的 excess phase 过量相移效应,即实际中,当频率升高,基极区域存储的少数载流子需要时间来扩散和漂移过基极,这个过程会产生额外的延迟,导致相位的额外滞后。该效应会让系统表现为分布系统,不能简单用并联 RC 表示。因此上面的方法适用于“并联 RC 模型成立”的器件,不是万能的

非静态工作点的 AC 分析

AC 分析不一定非要在“静态工作点”做。

**Slew-rate limiting(压摆率限制)**是指一个电子电路(最常见于运放 Op-amp 或放大器)限制其输出电压变化速度的能力。当输入信号变化太快,超过了电路内部能够驱动输出电荷的速度时,输出电压就无法准确跟随输入信号的变化,从而产生失真。当运放进入该状态时,电平还未达到稳定状态,此时小信号频率响应发生巨大变化而且正、负方向还不对称

非静态工作点 AC 分析的 Spectre 技巧

- 先跑 transient

- 停在某个时间点

- 用

prevoppoint=yes - 在这个非静态点上线性化

差分放大器 AC 分析

差分放大器的 AC 分析本质上是对“包含反馈的闭环线性系统”进行频域传递矩阵分析;通过 balun 将单端端口映射到差模 / 共模坐标系,从而研究不同模态下的增益、带宽与耦合。

在某个 DC 工作点线性化以后,差分放大器就是一个线性多端口系统。

本质是:

- 这是一个 频率相关的传递矩阵

- 每个元素都是 AC 分析算出来的

- 在不同频率有不同增益

这里引入差分放大器,是为了强调:

AC 分析 = 对线性化系统的“端口行为”进行测量

而差分放大器有一个问题是:

它天然就不是“单端口 / 单通道”的系统

所以不能用单端增益的思维去看它

对一个差分放大器做 AC 分析:

- 差模和共模必须分开看,如果直接在两个端口各加一个源,直接测量输出,得到的结果没有物理意义

- 差分系统也不是“两个单端系统的叠加”,因为共模反馈、尾电流源、负载耦合都会让左右两边强烈耦合

- 差模 <-> 共模“转换”是一个真实存在的通道

AC 分析永远是单端端口的线性求解;差模 / 共模不是分析类型,而是端口定义方式。

YZHG 是“端口行为”的描述,差分/共模是“物理模式”的描述,在差分放大器里:

- 工程师 更关心模式

- 而不是“某个端口的等效阻抗”

AC 分析总结

AC 分析的能力边界

AC 分析算的是什么?

AC analyses compute the small-signal sinusoidal steady-state response

也就是:小信号、正弦、稳态、线性化后的系统,AC = 频域线性传递函数

AC 分析不能干什么?

AC does not compute transient behavior

不能看瞬态稳定性

所以:

- 相位裕度 ≠ 一定稳定

- AC 看到的极点 ≠ 不会振铃

稳定性最终要靠 transient 或 XF 验证

cannot be applied where frequency conversion is significant

不能用于频率变换电路,比如:

- mixer

- chopping

- switched-capacitor(非准静态)

因为 AC 是 LTI 假设,而这些是 LTV / 非线性系统。

AC 分析的使用原则

The response computed by AC analysis is a simple linear function of the stimulus

所以,激励幅度本身没有物理意义。通常,幅度 = 1,相位 = 0

非线性效应不在 AC 里,失真、压缩、压摆率限制等

差分系统与 balun

差分系统更容易在差模 / 共模被分离后测量

也就是说:

- balun ≠ 特殊器件

- balun = 把端口变量变成物理模态

- 测量差模共模增益,及其输入输出阻抗和噪声,必须使用 balun

不同分析方法各司其职

-

什么时候用闭环测量?

闭环 AC:

- 低频 OK

- 高频 会被加载 / 双向耦合污染

-

什么时候要用理想受控源?

如果只关心运放本体而不是系统行为,那就:

- 用 VCVS / VCCS

- 隔离加载和反向通路

-

2-port 参数方法什么时候靠谱?

前提是:

- 接口定义清楚

- 不破坏工作点

- 不假设单向性

第四章:瞬态分析(Transient Analysis)

这一章节讲了瞬态分析要解决什么问题,以及为什么 transient 比 AC 难得多。

作者从三个板块介绍瞬态分析:

- 理论(theory)

- 瞬态分析的数学基础

- 离散化带来的误差

- 数值积分的本质

- 实践(practice)

- 误差如何累积

- 时间步如何选

- 哪些电路更“敏感”

- 应用(applications)

- 振荡器

- 正弦电路

- 储能电路

- 供电网络

transient analysis 的困难不是“方程复杂”,而是“数值误差 + 历史效应”。

瞬态理论简介

首先,作者先做一件非常重要的数学澄清:

非线性微分方程不能“整体”数值求解,只能逐点近似。

所以:

- 真正的解是:

- 连续时间的波形

- 计算机能做的是:

- 一串离散点

核心思想:

把时间轴切成一个个小时间步,每一步假设信号“足够简单”

这个“足够简单”就是:

- 一阶多项式(线性)

- 二阶多项式(抛物线)

作者用 最简单的 RC 电路,只为了说明:

数值积分 = 用差分近似导数

RC 方程:

用 forward Euler:

得到:

其中 是时间步

作者在这里刻意强调:

- 如果真实解是指数,而你假设是直线,那一定是近似

- 时间步越小,近似越好

积分法(Integration Methods)

首先定义什么是 integration method

用离散公式替代时间导数

在瞬态分析中,需要引入导数项,而导数通过与时间步长有关的差分近似,不同的积分方法对应不同的差分形式。对于电容,引入的是 ,由于电容值给定,可以等价为对电荷 的离散微分方程。采用梯形积分法后,电容可等效为一个等效电导和一个历史电流源,其等效电导乘以当前时间步的节点电压,再加上历史电流源,共同构成该器件在当前时间步对节点的电流注入。在 MNA 中,对每个节点将所有器件的电流注入贡献求和,并满足节点 KCL 条件,即注入电流之和为零。

SPICE 常用方法

-

Forward Euler

-

Backward Euler

-

Trapezoidal

-

Gear(Backward Difference Formula)

作者在这里没有评价谁好谁坏,只是说:

- Euler:一阶

- Trapezoidal:二阶

- Gear:任意阶(但 SPICE 只用低阶)

前向和后向欧拉好理解,前向用的历史项斜率,后向用的当前时间步斜率,前者显式后者隐式(需要求解当前时间步的微分方程)。如何理解 Trapezoidal 和 Gear 呢?

对于 Trapezoidal,数学上它就是:

也就是说:

- 不是只相信过去

- 也不是只相信未来

- 而是如果我用一条直线连起两个端点,那平均斜率就是它的真实斜率

Forward / Backward Euler 用“一个点”的斜率 -> 本质上偏向一侧 -> 会吃掉或放大能量

Trapezoidal 对时间是对称的,不偏过去,不偏未来,能量守恒近似成立,但它会振铃,因为:

- 它完全不阻尼

- 数值误差没有被“吸掉”

- 一旦有 stiff pole 或突变 -> 误差来回反弹

所以 Trapezoidal 是物理正确,但数值不宽容

现在来讲 Gear 算法,一种用于求解刚性常微分方程(DAE/ODE)的多步数值积分方法,该方法直接用多项式插值来逼近导数,用 次拉格朗日插值多项式(GearN)的导数去近似真实导数,算法细节如下(以 Gear2 为例):

-

假定我们知道一、二阶的历史项 ,加上当前项 作为插值,我们想获取关于这些插值的函数(唯一一条二次多项式)

满足:

-

我们虽然可以解该方程求 的值,但拉格朗日给了一个直接写出多项式的构造法,即拉格朗日基函数:

核心思想:用“单位响应”拼函数

我们想写:

希望做到:

- 在 :只剩

- 在 :只剩

- …

于是定义一组函数 ,满足:

这种函数就叫 拉格朗日基函数。

如果这样的 存在,那么:

因此在 :

完全不需要解方程

-

拉格朗日基函数的具体形式如下,给定节点:

拉格朗日基函数定义为:

为什么它满足“在自己点是 1,其它点是 0”?

- 当 ,分子里有一项 -> 整个乘积为 0

- 当 ,每一项变成 -> 整体为 1

这就是 基函数 的意思:“它在自己的节点上是 1,在别的节点上是 0”

-

时间轴平移 + 归一化,定义

于是

实际时间 归一化时间 … … 用 次拉格朗日插值多项式的导数去近似真实导数,即用最近 个时间点 对 做 n 次多项式插值,找到函数再求导:

- :已知的历史电压

- :在 为 1,其它节点为 0

-

Gear2:用 做二次插值。节点是 。

写出基函数:

求导并代入 :

所以:

各种积分法的特点

梯形法(Trapezoidal)和二阶后向差分(Gear2)是电路仿真中使用最广泛的积分法,更高阶的后向差分公式也有但很少使用。在某些情况下,例如第一个时间步和断点处(在输入波形的每个拐角处都会生成断点),SPICE 也会使用后向欧拉法。前向欧拉法在一些时序仿真器中使用,但在SPICE 等电路仿真器中则不使用。

如何理解第一个时间步和断点处,SPICE 使用后向欧拉法?

瞬态仿真时间轴是这样的:

- :初始时刻(由

.ic、.op或 DC 工作点得到)- :第一个时间步

关键问题

高阶积分法(Trapezoidal / Gear2 / GearN)需要历史点:

- Trapezoidal:需要

- Gear2:需要

- GearN:需要 N 个历史点

但在第一个时间步 :

- 只有

- 历史点不够

- 高阶方法数学上用不了

所以 SPICE 的做法是:第一个时间步,强制使用一阶后向欧拉(BE)来“起步”,这是数值积分里的启动(startup)策略。

至于断点,断点不是数值算法自己产生的,而是 电路激励强制指定的时间点,例如:

- PULSE 的上升沿 / 下降沿

- PWL 波形的拐点

- Verilog-A 中的

@(timer(...))- 用户

.tran ... strobeperiod或内部事件比如:

在这些时刻:

- 输入电压 不连续

- 或导数突然变化(阶跃 / 折线)

这些时刻就是 breakpoint

在断点处也要用后向欧拉,是因为 / Gear 的前提假设是被积分变量在时间上平滑,至少函数连续,最好导数连续。而在断点处波形突变,导数不存在或者剧烈变化,这会导致高阶方法产生数值振荡,出现非物理的振铃甚至牛顿迭代不收敛。因此断点处用后向欧拉,数值阻尼强,不追求高阶精度,不会产生振荡。

SPICE 的工程策略是在断点处临时退化为后向欧拉一步,等波形重新变平滑,再切回 Trapezoidal/GearN

对于固定的时步,就局部精度而言,这些方法中最准确的是 Trapezoidal,其次是 Gear2。然而,电路模拟器会自动控制时步以保持可接受的误差水平,因此无法提前确定对于特定电路哪种方法更准确,但 Trapezoidal 通常允许更大的时步,从而缩短运行时间。不幸的是,Trapezoidal 对先前时步的误差过于敏感,因此当相对容差较宽松时,它通常不是最佳选择。

向后欧拉法和 Trapezoidal 都是一步法,这意味着它们利用当前时间点的值来计算下一个时间点的值。GearN 是 N 步法,这意味着它需要 N 个前驱值。因此,后向欧拉和 Trapezoidal 能更快适应信号的突然变化,其中后向欧拉法的适应速度甚至比梯形法则更快(这也是在每个断点之后使用后向欧拉法的一个原因)。在计算具有许多突变的信号时,随着 N 的增大,N 步方法的效率会越来越低。

当容差要求严格或计算非常平滑的波形时,高阶向后差分公式是高效的。例如,生成正弦波或近似正弦波信号的电路。因为高阶多项式允许使用更大的时间步长而不会牺牲精度。然而,高阶 Gear 方法在轻度阻尼电路中可能会出现稳定性问题,也从未得到广泛应用。

刚性电路(Stiff Circuit)

在 EDA(如 SPICE 仿真)领域,“Stiff Circuit” 指的是物理意义上包含多时间尺度的电路

- 现象:电路中既有极快的瞬变(如纳秒级的开关毛刺),又有极慢的演变(如毫秒级的电容充电)。

- 数学定义:描述该电路的常微分方程(ODE)具有巨大的刚性比(Stiffness Ratio),即雅可比矩阵的最大特征值与最小特征值之比非常大。

- 仿真难题:普通的显式算法(如显式欧拉法)为了保证稳定性,被迫使用极微小的步长去计算那些已经平稳的部分,导致仿真速度极其缓慢甚至报错。

- 解决方案:必须使用专门的刚性求解器(Stiff Solver),如 Gear 方法(BDF)或隐式龙格-库塔法(Implicit RK)。

这里作者用了一个最简单的线性 RC 电路来探索不同积分法之间的特征差异

对该电路列 KCL:

采用后向欧拉法对时间离散表示导数,假定时间步长均匀,

可以得到差分方程

采用前向欧拉法,得到的差分方程是

对于不同的 ,用不同的积分法计算 ,

|

|

|---|---|

|

|

可以看到,前向欧拉法在 时就产生了振荡, 时甚至还能以指数增长(不稳定不收敛)。较大的 表示与时间步长相比非常小的时间常数(RC)。这类电路被认为是刚性的,可能会给积分方法带来问题()。对于刚性电路,向后欧拉法和 Gear2 法表现良好,而梯形法则会出现明显的点对点振铃现象。另外,对于时间常数略小于时间步长的情况,Gear2 法会出现轻微的过冲。

一般而言,物理系统,尤其是电气电路,存在许多高频极点,这些极点在系统响应中通常不起重要作用,要么是因为它们从未被激发,要么是因为由这些极点引起的任何瞬态变化衰减得非常快。因此,模拟器所采用的时间步长通常会远大于与这些极点相关的时间常数,所以电路往往是刚性的。若要将前向欧拉法应用于这样的电路,则必须将时间步长缩小到小于电路中存在的最小时间常数。因此,对于刚性电路而言,采用前向欧拉法的效率远低于采用刚性稳定方法。换句话说,刚性稳定方法的时间步长受到限制以保证精度。而对于前向欧拉法以及其他非刚性稳定方法,时间步长的限制既要保证精度又要保证稳定性。大部分电路往往非常刚性,因此稳定性约束常常要求其时间步长比精度要求小得多。出于这些原因,在电路模拟器中很少使用非刚性稳定的积分法。

根据 z 平面映射关系分析稳定性

本节通过研究连续时间系统在拉普拉斯域(s-plane)中的稳定极点,分析不同数值积分方法的稳定性。连续时间系统的稳定性由其自然响应中的指数因子 决定,只有当所有极点满足 时,系统的响应才会随时间衰减并保持稳定。

由于拉普拉斯变换描述的是连续时间系统,而数值积分法实际采用的是离散时间差分形式,因此每一种积分方法都会隐式地定义一个从 -域到 -域的极点映射关系。通过在 -域中考察该映射下,连续系统稳定区域()内的所有极点是否始终落在单位圆 内,可以判断该积分方法在任意步长下是否保持稳定。

若连续系统的整个稳定区域在映射后均位于单位圆内部,则该数值积分方法被称为无条件稳定(A-stable)。

这里要回顾一些工程数学上的基础:

拉普拉斯变换的定义包含 项,相对于傅里叶变换,不仅考虑了各频率分量的占比,又考虑了幅度的衰减/增长因子。

拉普拉斯变换是针对连续信号的,它对应的离散版本是 z 变换,因为离散信号拉普拉斯变换的形式为:

为了简化计算引入了 ,这样就把复杂的指数运算变成了简单的代数多项式运算。

虽然拉普拉斯变换也能处理离散信号,但其结果是周期性的,分析极点不直观。通过 z 变换,s 平面左半平面被映射到了 z 平面单位圆内部,稳定性判定更直观,频率响应更清晰,因为傅里叶变换在 s 平面是虚轴,但在 z 平面中变成了旋转的单位圆。

首先对显式欧拉(前向欧拉)做映射关系,前面推导过了

因此这里的极点 ,且由于 ,当 时极点跑到单位圆外面去了,该方法不稳定。

然后是隐式欧拉(后向欧拉),前面推导的结果

因此这里的极点 ,该极点对于任意时间步长 始终落在单位圆内,该方法无条件稳定。

Trapezoidal(梯形法)

差分(平均斜率):

得到:

因此:

该方法稳定性有保证(极点落于单位圆内),但 时产生振铃(无高频阻尼)

这里涉及到了一个关键词:高频阻尼。为什么需要这个高频阻尼,它虽然和离散信号处理中低通滤波器作用类似,但本质却截然不同。

拉普拉斯变换与傅里叶变换的本质区别是多了个数值阻尼项,也就是复指数的实部,该实部决定了复指数幅值的衰减率。理想情况下,高频阻尼是不存在的,因为能量守恒幅值保持恒定。但我们研究对象的方式是时间离散的,即通过时间步来描述不同时刻下系统的动力学行为。那么这就存在一个问题:时间步内系统的动力学行为还需要关注么?答案是不需要,在时间步内即便系统发生了翻天覆地的变化,我们也认为该时间步对应的两个时间点之间的系统变化是线性的或者平滑的。这种处理方式本质上就是在对高频进行衰减,即高频阻尼。对于数值阻尼,相比低通滤波器有如下本质区别:

数值阻尼不是为了“还原真实基带信号”,而是为了在“无法解析的时间尺度”上,选择一种“物理上更合理的错误处理方式”。

这句话里有三层关键词:

- 误差一定会产生(不可避免)

- 误差主要集中在“解析不了的快模态”

- 数值阻尼不是在“修复”,而是在“裁决”

误差的产生,源自于你能分辨的最高时间分辨率,任何时间尺度小于时间步的变化,对我们来说都是不可区分的。

连续系统中必定存在“快模态”,例如寄生LC,高Q谐振,切换边沿,非线性瞬态。这些模态真实存在但我们选取的时间步看不清细节,我们对时间做离散化的时候,例如梯形法

梯形法是一种时间可逆、无数值耗散的双线性离散化方法。对于连续系统中的纯虚极点 ,梯形法会将其严格映射到 平面的单位圆上,因此在离散系统中振荡模态的幅值不会随时间衰减。尽管这种方法会引入频率扭曲,但不会对振荡能量产生数值耗散。由于数值计算中的截断误差、舍入误差或事件不对齐误差无法被衰减,这些误差容易在高 Q 振荡模态中长期保留,从而在实际仿真中表现为振铃等非物理现象。

对于后向欧拉

且随着频率的升高, 单调减小,表明后向欧拉法对高频振荡模态引入了较强的数值阻尼。该方法因此具有良好的数值稳定性,能够有效抑制高频数值振荡。然而,这种阻尼会削弱系统的快速动态响应,使瞬态变化被平滑化,从而降低对高频或快速变化过程的分辨能力。

二阶后向差分法(Gear2)

两边同时做 z 变换

获取极点在 z 域中的映射情况,同样也可以计算出 ,可以断定 Gear2 法也是无条件稳定的

不同积分法在 z 平面的映射关系

|

|

|---|---|

|

|

以上都是稳定的积分法,不稳定的显式欧拉则有部分不在单位圆内

人工数值阻尼

这里要更深入地了解所谓的阻尼是什么。当时间步开始接近电路中的特征时间,例如 RC 时,计算结果已经开始变得不可靠了,“物理正确解”这个概念本身就已经失效了,原因很简单:

- 连续系统在 一个时间步内 已经发生了主要动力学变化

- 你却只采样 一个点

- 此时任何离散算法:

- 要么 篡改物理

- 要么 暴露不适定性

隐式欧拉在时间步接近或超过特征时间时,会物理等效为 RC 并联一个巨大的数值电阻,也就是我们看到的“平滑、单调、不振荡”,但这并不是 RC 自己的行为,而是 RC + 人工阻尼网络,这不是“物理正确”,而是不管你真实怎么变,反正都给你耗散掉。

梯形法做了三件事:不加耗散,不隐藏误差,不替你稳定系统。它会使误差以振铃的方式来回翻转,因为没有给它足够的时间分辨率。

阻尼的存在有好有坏,数值阻尼本身没有对错,它是一种工程妥协:

用物理保真度换取数值稳定性与可计算性。

阻尼太小 -> 振铃、时间步被逼得极小、仿真跑不完

阻尼太大 -> 波形好看、仿真能跑完,但真实振荡可能被抹掉

当真实的振荡(ringing)幅度相对于直流值很小的时候,仿真器的误差控制会被“大信号”主导,从而允许时间步长变得很大;一旦时间步变大,像隐式欧拉 / Gear 这样的算法会引入极强的人工数值阻尼,于是这些小而真实的振荡就被“数值阻尼淹没”,在结果中消失。

尤其是像感应电源总线和时钟线这种地方,因为这些地方:

- 高 Q 的寄生 RLC

- 振荡是真实存在的

- 但幅度往往只有 mV 级

- DC 电平却是几百 mV ~ 1 V

由于 SPICE 用的是相对误差控制,在默认 reltol = 1e-3 下,模拟器会认为误差已经足够小了,不需要再减小时间步。在这种大时间步下,隐式欧拉 / Gear 的人工数值阻尼变得极强,从而把这些小而真实的振荡数值性地抹掉。

高阻尼什么时候是“好事”?

目标:仿真能跑完

典型场景:

- 大规模电路(PDN、SoC、SerDes 前端)

- 只关心:

- DC

- 平均值

- 大信号趋势

- 不关心:

- mV 级振铃

- 高频瞬态细节

数值表现:

- 隐式欧拉 / Gear2

- 大时间步

- 波形平滑

工程含义:

牺牲高频真实性,换可计算性

低阻尼什么时候是“好事”?

目标:不篡改物理

典型场景:

- 振荡器、LC、时钟网络

- PDN 共振分析

- EMI / SI / jitter / SSN

- FFT / 频谱分析前的瞬态

数值表现:

- 梯形法

- 小时间步

- 可能振铃、慢

工程含义:

让所有误差和真实振荡都“活着”

振铃

在“刚性电路(stiff circuits)”中,梯形法会产生一种误差:每一个时间步,误差符号都会交替变化。

关键点有三个:

- 不是解本身错

- 误差在正负之间来回翻转

- 幅值仍然在误差容限(reltol / abstol)之内

这就是所谓的 trapezoidal ringing,梯形法振铃

仿真器认为:没超误差,没不收敛

但工程师看到的是:波形在抖,FFT 有噪声底,电流/电压异常大。

仿真器觉得没问题,但用它做分析会出错

为什么梯形法振铃有问题?

-

不能做 FFT

因为梯形法振铃本质上是人工引入的高频,接近 Nyquist 的数值噪声

-

电容电流 / 电感电压特别糟糕

梯形法在状态变量(节点电压、电感电流)上误差还可控,但由于电容电流 / 电感电压本质是求导得来的,梯形法振铃在电容电流、电感电压上会被“放大成灾难”

-

小时间步时反而更明显

梯形法的误差是高频交替误差,时间步越小,Nyquist 频率越高,就越“看得见”这种抖动

-

梯形法振铃 ≠ 只是“波形不好看”,它会让误差永远不满足,逼迫时间步趋于0,让仿真几乎跑不完

当瞬态仿真异常慢的时候,不要先看所有节点,而是先画供电电流(supply current),因为供电电流是所有高频误差的“汇总输出口”

总的来说,梯形法振铃是一个“数值上合法、物理上有害”的现象。它不会让仿真报错,却会污染频谱、放大导数误差、拖慢仿真;Gear2 能消掉它,但只是牺牲物理真实性换工程可行性。

电容电流与电感电压

电容电流和电感电压本质上是“对状态变量求导”的量,它们比电容电压、电感电流更容易放大数值误差;而 SPICE 在计算它们时,往往并没有用和状态变量同样可靠的积分框架。数值分析里有一条铁律:微分会放大误差,积分会平均误差。因此电容的电压波形还算平滑、可信,但电容电流的任何微小抖动都会被放大。

MNA 中有一个很关键但容易被忽略的点:

电容电流和电感电压不是状态变量

这意味着时间步控制(reltol)主要关注节点电压和电感电流,不关心电容电流和电感电压的误差。且由于电容电流和电感电压不会积累,所以时间步控制完全可能忽略掉它们。这会导致你看到的结果数值上已经很糟,但仿真器毫无察觉。

SPICE 中计算电容电流的方式也很差,算电压时用解隐式微分方程的方法,算电流时则事后用简单的差分求导。

用 MOS 栅电容做例子,它有三个“专门用来坑数值算法”的特性:

- 门极电压是连续 ramp

- MOS 的栅电容会突然消失 / 出现

- 电流的变化是“非同步、不对齐时间步”的

针对上面的例子,存在第一个问题:电流突变“不在时间点上”

这里所谓的不在时间点上,指的是电流的突变不是由设定的独立源引起的,仿真器不知道这里应该插一个时间点。由此导致的结果是转折点被错过,该位置处的导数发生突变,波形看起来像被敲了一下。

需要注意的是:任何积分法都会遇到这个问题。导致这个问题的根本原因是事件未对齐时间网格,仿真器无法感知器件内部导数的快速变化,因此未能在该处细化时间步,而仍以远大于该变化时间尺度的时间步进行差分计算,导致局部导数估计严重失真。

为什么梯形法容易振铃?

对于电感电流:

梯形法离散后:

假设电压不变或变化极小(所以物理电流应为 0)

那公式变成:

由此产生的任何一次电流误差,都会在后续的时间步中以正负交替的形式永久存在,这就是 point-to-point ringing 的数学根源!

这种误差的来源可能是(一个就够了):

- MOS 电容突变

- 数值导数不精确

- 转折点未对齐时间步

为什么 SPICE/Spectre 在断点后切换到隐式欧拉?

之所以在断点后,SPICE 会切换并使用一步隐式欧拉,目的就是为了利用巨大的高频阻尼消除掉刚刚注入的高频误差。但问题是,触发该切换行为的必须是独立源,而非器件内部非线性。假如器件内部非线性过程非常快,远小于差分时间步,仿真器仍会默认该位置继续使用大尺度时间计算,于是梯形法的振铃现象就无法避免。

对于 Gear2 积分法,由于多了一个历史项,它的效果是抑制高频、强调低频。因此对于梯形法和 Gear2 法

梯形法:

- 一开始准确

- 一旦错,永久记住错误

Gear2:

- 一开始就有误差(3/2 因子)

- 但 不会记住高频错误

就结果而言,隐式欧拉看上去貌似效果最好,但它的副作用是时间延迟。它的问题是:

- 引入 约 0.5 个时间步的相位延迟

- 在正弦电流中体现为相位偏移

但关键是,BE 不是每步都用,只在断点附近用,所以延迟是局部的

在这里,作者演示了两种断点处理,一种是 Gear -> BE -> Gear,一种是 Trapezoidal -> BE -> Trapezoidal。分析电路如下

测试电路直观上是两个相互独立的电路,理论上 的电压不应影响 的电流。但实际仿真过程中,两套电路是受同一个仿真器控制的,因此当 电压遇到断点时, 所在电路的积分法也会跟着改变。

可以看到, 的电压是连续正弦信号,对应电容电流也应是连续平滑的正弦电流。但当 电压遇到断点时,积分法发生切换,从 Gear 切换到了 BE,此时就会引入一个局部的相位延迟,然后重新切换回 Gear,就会导致波形在断点处出现小鼓包。从中可以看到,每次断点处 BE 引入的相位延迟不会积累,即不会和下一个断点处的延迟叠加。这就是阻尼带来的好处,会让电路自身消耗掉计算引入的误差,但又要合理控制阻尼的大小,避免阻尼过高影响计算精度。

Trapezoidal -> BE -> Trapezoidal 的处理结果如下

可以看到这里仅有一个断点,却让后面的波形一直处于振铃的状态。这就是因为梯形法没有阻尼,从而一直保持断点引入的计算误差且无法自行衰减。如果有第二个断点,误差就会叠加直到计算结果乱七八糟。

截断误差(Truncation Error)

什么是截断误差(Truncation Error)

- 本质:用离散差分近似连续导数所引入的误差

- 分两类:

- LTE(Local Truncation Error)

单个时间步产生的误差(假设之前都对) - GTE(Global Truncation Error)

多个时间步误差累积后的最大误差

- LTE(Local Truncation Error)

关键点不是“每一步有多准”,而是:

误差会不会在电路里被放大、保留、或者自然消失

GTE 的大小,主要由电路本身决定,而不是积分方法决定。也就是说,同样的数值误差,在不同电路中,有的立刻消失,有的永久保留,有的被不断放大。

因此这里涉及到一个核心概念:电路对误差的敏感性

所谓的电路敏感性,就是如果我在某一时刻注入一个很小的误差,它会“消失?”,“持续?”,还是“越变越大?”的问题,这不是数值问题,是系统动力学问题。

因此可以将电路根据敏感性分为:

-

不敏感电路(误差会消失)

- 例如逻辑/偏置/RC电路

- 有有限时间常数

- 有耗散

- 有恢复机制

- 对于单次误差,误差被系统指数衰减掉;对于连续误差,稳态发生偏移,但状态不发生爆炸

- 误差最终都会被系统“吃掉”

- 例如逻辑/偏置/RC电路

-

高敏感电路(误差会被保留或放大)

-

例如 LC 振荡器

- 无耗散(不含任何阻尼元件,误差会积累)

- 相位极其敏感,有一点点偏差都会导致结果产生严重错误

-

书上的在 LC 振荡器的第十个周期结束时,添加了一个大小相等、方向相反的激励,理论上相位抵消,振荡完全停止。而实际上由于前面误差的积累,导致理论上第十个周期的结束时间与计算包含误差的时间点没对齐,从而振荡继续存在。

SPICE2 计算的包含误差的 LC 振荡电压

-

例如纯电容电路

- 极点在0且时间常数趋于无穷

- 单次误差会永久保留,连续误差导致电压线性偏移

- 成为了一个误差存储器

-

| 电路类型 | 误差命运 |

|---|---|

| RC / 有损系统 | 衰减 |

| LC / 振荡器 | 长期存在(相位决定) |

| 纯 C / 积分器 | 永久累积 |

| 混沌 / 采样保持 | 指数放大 |

局部截断误差(LTE)源于在有限的时间步长内对电路进行分析,即各种积分法用差分或代数式替代导数项。通常,更多的时间步意味着时间步长越短,误差越小,但仍需谨慎选择,因为瞬态分析的精度很难估计,取决于所模拟电路的类型。

LTE 的阶数关系

-

Backward Euler(一阶)

-

Trapezoidal / Gear2(二阶)

小步长下,高阶方法确实更准。但:

- 常值波形 -> 没有截断误差

- 时间常数 > 平衡点精度

也就是说:

截断误差会影响时间常数,如稳定时间和振荡周期,但不会影响直流值或稳定值,除非这些值取决于时间常数。如果更关注精确找到平衡点,而时间常数的精度并非至关重要,那么可以通过收紧 reltol 来获得精确结果,并通过放宽 trtol(在 Spectre 中为 lteratio)来加快仿真速度。

电荷守恒

电荷守恒为什么重要?

- MOS 模型是 电容模型

- 每个时间步:

- 电荷被创建 / 转移 / 消除

如果模型或算法不守恒:每个时间步一个很小的错误 -> 在存储型电路中会无限积累。

即便模型守恒:

- 数值收敛误差

- 时间步误差

仍然可能导致仿真器层面的“非物理电荷泄漏 / 注入”

如果电容/器件模型不是从“电荷函数”推导出来的,而只是给了“电容 = dq/dv”, 那么在瞬态仿真中,电荷一般是不守恒的;误差不会因为时间步变小而消失,只会变慢。

满足电荷守恒理论上应该发生什么?

- 输入刺激最后回到 0

- 所有电容:

- 充电 -> 放电

- 净电荷 = 0

- 所以输出最终应回到 0

实际在 SPICE 里发生了什么?

- 输出 没有回到 0

- 出现 残余偏置

- 这是:

- 没有任何物理依据的

- 纯数值产物

这不是数值积分误差,而是“凭空造电荷”

换成 Spectre + 电荷守恒模型

- 输出几乎回到 0

- 再把

reltol收紧:- 偏差彻底消失

说明:

- 模型是否守恒,决定误差能否“原则上消失”

- 时间步 / 容差只决定“误差有多快显现”

为什么“电容模型”会不守恒?

-

电荷模型先定义点和函数

再由此得到电流

因此只要电压回到原点,电荷一定会回到原点,与路径无关,回到原点的偏差与时间步/容差有关

-

但对于电容模型

数值上用的是差分近似

这意味着当 随 发生非线性变化时,前进一步差分结果得到的 与退回同样一步差分结果的 之和不等于零。由此导致积分结果与路径相关,电荷不守恒。

因此,基于电容的模型,电压轨迹每一步产生的微小误差会累积起来,最终电荷值不会等于初始电荷值。

电容模型满足电荷守恒的条件

以 MOSFET 为例,考虑栅极流向源极的电荷,该电荷为栅源电压 ,栅漏电压 和栅体电压 的函数 ,总电荷的环路积分为

其中 为电压矢量,带入上式得

由此可以看出,左边是一个围道积分,利用斯托克斯公式将其转化为曲面积分

将旋度展开

考虑到电荷守恒,即该围道积分与路径无关,且 连续可导,其二阶导应对称,因此上式三行对应的项都应为零,有

这个就是满足电荷守恒的条件,即所有电容必须来自同一个“势函数”(电荷势),不能各算各的。

假如模型

- 只给了

- 忽略 的耦合导数

这样数学上:

- 二阶偏导不对称

- 不存在任何 能生成这些电容

由此导致围道积分与路径有关,电荷不守恒,该模型就天生带有不可修复的结构缺陷。

步长控制

瞬态仿真的成败,90% 取决于时间步控制(time-step control),而不是选了什么积分公式。

仿真器如何决定“下一步时间该走多大”?这直接决定了:

- 是否漏掉快速事件

- 是否出现梯形法振铃

- 是否引入过度数值阻尼

- 是否算得慢到跑不完

SPICE / Spectre 会根据前几个时间步的状态变量(电容的电荷或电感的磁通),用多项式外推得到当前时间点的预测值,再与通过 MNA + Newton 实际求解得到的结果比较;若该差值超过由 reltol、trtol 以及 chgtol / abstol 决定的 LTE 阈值,就减小时间步。

SPICE 的时间步参数到底在干什么?

这里需要提一句截断误差是如何计算的,核心思想在于用“多步法的多项式外推预测值”与“真实计算值”的差,来估算“如果时间步再大一点会错多少”。对于电容的 MNA 方程,表面上是电压的微分,实际上电压乘以电容就是电荷,因此就是电荷的微分方程,电荷也就等同于电容电压是一种状态变量。同样对于电感,磁通等同于电感电流是一种状态变量。

SPICE 将这些历史状态变量保存下来,用积分法的方式拟合并外推一个预测值 ,这一步是纯数学预测,不需要求解电路。真正求解电路(MNA + Newton)得到的结果作为真实值 ,与预测值做差得到得到截断误差 LTE

SPICE 会对每一个电容 / 电感算一个 LTE,然后:

允许误差通常是:

或类似形式。

reltol:相对误差容忍chgtol:小电荷下的绝对保护

只要有一个器件不满足,就会将时间步缩小

trtol 决定了时间步下次走多大,它控制的是在 LTE 已经合格的前提下, 下一步时间步可以“放松”到什么程度。

典型逻辑(概念式)是:

其中:

- :积分方法阶数(Trap/Gear2 → 2)

trtol:安全因子(safety factor)

注意这里的位置 trtol 是乘在时间步更新公式上的,而不是乘在误差容限上。

-

reltol—— 总控旋钮(最重要)- 控制:

- Newton 收敛(允许误差)

- LTE 判据()

- 越小 -> 越准 -> 越慢

想要更真实的瞬态细节,先调 reltol。由于是相对误差,必须“相对于某个量”,三种选择:

标准 含义 global 全电路历史最大电压 local 每个节点的历史最大电压 point-local 当前时刻该节点电压 global 最宽松,point-local 最保守,没有绝对对错,取决于电路。对于小信号节点 + 大电源节点,用 global 会完全放松小信号节点的约束,导致严重错误。

- 控制:

-

trtol—— LTE 相对 Newton(允许误差)的权重- 只影响 LTE

- 默认值 7,不要随便减小

- 减小

trtol而不动reltol:- 会逼仿真器追数值噪声(

reltol决定了 LTE 判据,在数值误差不变下提高计算精度只会算出更精确的误差) - 反而更慢、更假

- 会逼仿真器追数值噪声(

工程经验:不要让 LTE 判据比 Newton 判据更严

-

Tmax—— 时间步上限默认:

也就是说整段仿真至少 50 个时间点

这对以下情况是灾难:

- 多周期振荡

- 高 Q LC

- 时钟 / 串行链路

作者明确建议:如果仿真超过 10 个周期,应该收紧

reltol、chgtol、Tmax -

abstol/chgtol—— “小信号保护”参数 控制什么 abstol小电流 / 小电压下的 LTE chgtol小电荷 / 小磁通下的 LTE 这两个决定是否会“看不见小振荡”,如果

chgtol/abstol太松,小振荡会被数值阻尼抹掉。

SPICE vs Spectre 的本质差别

SPICE 的哲学

- 控制 电荷误差

- 对电压是间接控制

- LTE 判据偏松

- 容易梯形法振铃,漏掉快速边沿

Spectre 的哲学

- 直接控制 电压误差

- LTE 判据是:

- 更贴近用户真正关心的输出量

所以大多数情况下,Spectre 的时间步控制比 SPICE 更谨慎。接着作者通过 DAC 波形和 MOS 松弛振荡器两个例子证明了时间步控制和 LTE 控制的重要性。

误差预设(Error Preset)

前面步长控制中用到了许多超参数,如果不想一个一个调 reltol、maxstep、method 该怎么办?

Spectre 给了一个工程化旋钮:errpreset。它有三个挡位:

| 模式 | 本质 |

|---|---|

| liberal | 快、松、容易错 |

| moderate | 默认,工程折中 |

| conservative | 慢、稳、最可信 |

它会同时预设:

- reltol

- iteratio

- relref

- 积分方法(trap / gear)

- maxstep

其实就是一套参数组合模板。

断点(Break Point)

为什么仿真器非要在波形拐角处停一下?

什么是 break point?

- 波形 斜率不连续 的地方

- 仿真器 强制插时间点

- 不允许跨过

会产生 break point 的情况:

- PULSE 的每个边沿

- PWL(Piecewise Linear) 的每个点

- 正弦源开始

- 指数源的时间常数起点

- 传输线延迟

为什么必须这样?

否则会:

- 错过短脉冲

- 把尖峰“跨过去”

- 完全算不出来

break point ≠ LTE,它是结构性时间点约束。

传输线中的断点问题

传输线中需要使用断点控制时间步长,如果未使用断点来控制时间步长,那么波形的尖角可能会被削平,或者短脉冲事件可能会完全消失。为避免这种情况,传输线会自动生成其自身的延迟断点。

当电路中包含多条传输线时,断点带来一个严重问题,断点时间间隔为多条传输线的时间公约数。如果这个数远小于瞬态分析的时间,生成的断点数量可能会极其庞大,从而使电路难以进行仿真。新 SPICE / Spectre 通过动态生成 + 合并的方式避免预生成断点,但断点太多的时候需要用算法来过滤生成的断点,判断哪些断点重要,哪些不重要,因此高速链路仿真会很慢。

若阻抗失配,传输线的近端和远端会产生电压反射,由此造成一系列电压断点。若存在多根长短不一且不匹配的传输线,会产生大量断点,严重影响仿真计算。

旁路(Bypass)

旁路加速技术的核心想法是:

如果一个非线性器件的端电压没怎么变,能不能复用上一次算好的电流?

想法是挺好的,但也存在很多问题:

- 要存大量历史状态

- bypass/un-bypass 会引入不连续

- 由此注入数值噪声,影响 FFT 的计算,浪费大量内存,甚至影响收敛

因此作者认为此项技术看起来很美好,但大多数时候不值得使用。Spectre 就没用这个机制,是刻意而为的。

初始条件(Initial Condition)

初始条件是求解瞬态仿真的起点,解决初始条件问题,就是解决

瞬态仿真从哪里开始计算?

现实情况是

- 微分方程 -> 需要完整初始条件

- 但用户 -> 只给了一部分

SPICE 的折中方案

- 默认:

- 先做 DC

- DC 解作为初始条件

UIC(Use Initial Conditions):- 跳过 DC(用户指定的初始电压/电流值来启动瞬态仿真)

- 用 backward Euler 推第一步

存在的根本难点在于:

- 电容 / 电感环 -> 初始条件可能冲突

- 节点 IC -> 不一定能唯一映射到器件 IC

有时用户会发现:

为什么“设了 IC”,仿真器却经常给你一个“不是你想要的初始状态”

-

SPICE 把“初始条件”变成一个“非常弱的强制源”

具体做法是:

- 电容初值 -> 用 Norton 等效:

- 一个电流源

- 串一个很小的电阻

- 电感初值 -> 用 Thevenin 等效:

- 一个电压源

- 并一个很小的电导

这个“小电阻 / 小电导”是关键问题来源。

- 电容初值 -> 用 Norton 等效:

-

只要存在“电容环”,SPICE 一定会“修改用户指定的初始条件”

原因是:

- 多个电容并联 / 成环

- 每个电容都有一个“弱强制源”

- 这些源在数值上是冲突的,不可能并联的两个电容同时有两个电压

- SPICE 的解法是按电容大小加权平均

-

Node IC 和 Capacitor IC 的本质差别

如果用

.ic V(node)=...- SPICE 反推出所有连接到该 node 的电容 IC

- 等价于:我不关心每个电容,只要节点电压对

这在电容环中是唯一相对可控的方式。

-

不用 UIC(先 DC)的模式,为什么“更稳但不精确”?

不用 UIC 时:

- SPICE 先做 DC 分析

- 用 1Ω 强制源把 node 拉到 IC

- 再释放,作为 transient 起点

问题是:

- 这个 1Ω 并不“足够小”

- 并联 LC 时,电感电流一定非零

- 会引入非物理初始能量

所以 DC-based IC 是“数值稳定优先”,不是“物理精确优先”

接着作者介绍了 Spectre 的 IC(为什么更好)

核心只有三条,但都很重要:

-

Spectre 支持“支路级 IC”

不像老 SPICE:

- 只能 node IC

- 电感 IC 很受限

Spectre 可以:

- 电容

- 电感

- 节点

- 支路

更接近“状态变量本身”

-

IC 可选择性启用(dc / tran / dev)

Spectre 允许指定:

- IC 只影响 transient

- 不污染 DC

- 不影响器件内部状态

这是 SPICE 做不到的。

-

rforce 可调(极重要)

前面看到的问题,本质都和“强制 IC 的等效电阻太大 / 太小”有关。

Spectre 允许:

- 调 rforce

- 控制“IC 的刚性”

这在高 Q、弱阻尼系统里是救命功能。

初始条件和节点集(Nodesets)的区别

Nodeset ≠ Initial Condition

| 项目 | Initial Condition | Nodeset |

|---|---|---|

| 定义真实初始状态 | ✅ | ❌ |

| 影响 transient 起点 | ✅ | ❌ |

| 影响 DC 解 | ❌ | ✅ |

| 本质 | 状态约束 | 收敛提示 |

nodeset 是“告诉牛顿往哪找解”,不是“告诉系统从哪开始”

准确性问题的解决办法

核心思想:

不要第一反应就“减时间步”。人为缩小时间步,往往更慢,不会更准,反而还可能更不稳定。

推荐的修复顺序(非常重要)

- 偏置是否正确(90% 的问题在这)

- 模型是否合理,尤其 MOS 电容

reltol- 使用 charge-conserving model

- 确保

gmin不影响解决方案。如果可能将gmin设为 0 - 如果出现 point-to-point ringing,方法切换梯形 -> Gear2。如果耗散过大,切回梯形法或收紧

retol - IC / UIC 问题,用 IC 语句调整 rforce 直到初始条件正确。若指定电容电感的初始条件,时域分析中指定 UIC

- 仿真振荡器要注意

maxstep,设置为预期振荡周期的十分之一或更小

“缩时间步”是靠后选项,不是首选

瞬态分析中的收敛性

这里有一个非常重要但反直觉的结论:

Transient 的收敛性,通常比 DC 好

原因:

- transient 是 continuation method

- 上一步解 ≈ 下一步解

所以如果 transient 不收敛,往往不是“数值问题”,而是模型不连续,电路不物理

导致不收敛的几个点:

不连续性

-

不连续的器件模型

典型例子:

- MOS channel 消失 -> gate C = 0

- BJT diffusion C 消失

- 没有 overlap / junction C

后果:

- 电压斜率 ->

- Newton 发散

- 时间步越小越糟

这不是数值问题,是模型错

-

没有电容到地路径的节点

真实电路:

- 没有真正的瞬时跳变

仿真电路:

- 理想模型 -> 跳变

工程补救:

- 加极小 C 到地

- 用

gmin

大容量浮置电容

这里是一个非常隐蔽但致命的数值问题

问题本质

- 超大电容,C 数值很大

- 悬浮节点,在 DC 中,该节点如果只连接电容,相当于短路,节点是悬空的,电导为零

- 很小时间步,分母很小

结果:

-

电压分辨率 ~ 1e-15 V(V 很小的波动就会导致绝大的瞬时电流计算值)

-

电流计算:

-

数值电流远大于容许误差

-

KCL 失败

-

Jacobian 奇异(电导矩阵对应的对角元素接近0)

解决方案

优先级顺序:

- 用更小的 C(物理优先)

- 把 C 接地

- 最后才是增大

abstol

不收敛时的补救措施

原则 1:消灭“非物理不连续性”

仿真器最怕的不是非线性,而是:

- 电容突然消失

- 电压/电流瞬时跳变

- Jacobian 瞬间奇异

所以你看到这些建议反复出现:

- MOSFET 必须给完整电容模型

- junction

- overlap

- 给 source / drain area(否则结电容 = 0)

- Spectre 用

cmin给每个节点接一个小电容到地 - 避免 large floating capacitors

- 必要时直接修改非线性电容模型

本质是让系统连续可微,牛顿法才能活

原则 2:数值自由度不足 -> 放宽“硬指标”

当模型已经“尽量物理”,但还是不收敛:

- 增大 Newton 最大迭代次数(itl4 / maxiter)

- 换积分法(Gear2 特别有效)

- 放宽绝对误差(abstol / iabstol)

- 最后才:

- 放宽 reltol

- 放宽 stimulus 边沿(让仿真“跳过去”)

这是在允许仿真器“不那么精确”来换取收敛

瞬态分析的应用

瞬态分析算 DC 工作点

为什么要用 transient 算 DC?

因为 DC Newton 不收敛,或模型太复杂

核心做法:

- 所有独立源从 0 慢慢 ramp 到 DC

- 跑 transient

- 取最后一个时间点作为 operating point

关键工程技巧

- 用 Backward Euler

- 关 LTE(

lvtlim=1) - 大步长(不追求波形,只要稳态)

- 如果振荡,先想办法 disable 振荡模式

Spectre 提供的高级选项:

skipdcskipdc=wavelessskipdc=rampup- 自动选择(

skipdc=autodc)

本质:这是“伪瞬态”,不是物理 transient,因为我们只关心最后稳态收敛的结果

振荡器(Oscillators)

振荡器为什么“必须人为启动”?

理论上:

- DC 解 = 平衡点

- 除非受到干扰,否则电路不会偏离平衡点

- 如果平衡点是稳定的,且干扰很小,那么电路在之后会回到平衡点

- 振荡器的平衡点不稳定

现实中:

- 热噪声

- 上电扰动

仿真中什么都没有

所以必须人为提供“扰动”,才能使振荡器偏离其平衡点,振荡才能够发生。一般来说,最好选择能最好地耦合到振荡模式,且对其他不希望出现的响应模式耦合最小的方法和位置。尤其要避免激发任何偏置电路中与之相关的极慢的时间常数。

哪些“启动方式”是烂的

-

用电源 ramp 启动(最常见错误)

对称电路(如 7-stage ring):

- 电源 ramp 是完全对称扰动,所有的 stage 同时受到相同的扰动

- 与振荡模态正交

- 结果:不起振

-

用 uic + IC 启动 LC / ECP 振荡器

- uic 的 IC 是靠:

- 电压源 + 小电阻

- 电流源 + 小电导

- 在 LC 里:

- 电感把这个“强制源”短掉

- 产生 巨大初始电流

- 结果:

- 非物理巨大振幅

- long settling

reltol被迫放松

这里给了两张图,是射极耦合对谐振器 ECP 示意图,和其通过

non-uic-based初始条件得到的结果这里解释一下为什么单独强调

non-uic-based,因为node IC+non-UIC时,SPICE 必须反推出电容电压和电感电流,这个反推过程一定会通过 DC 强制,引入数值源和小的串联电阻或并联电导。SPICE 会先通过 DC 分析和强制源来满足该初始条件,这称为non-UIC-based initial condition。这里给出的结果是极耦合对振荡器在 non-UIC-based 初始条件 下的响应。在这种情况下,用户通过

.ic指定了节点初始电压,但没有使用uic,SPICE 会先通过修改电路并引入强制源与小阻抗来构造一个满足初始条件的 DC / pseudo-DC 状态,然后再从该状态开始瞬态分析。这种方式本质上是存在问题的,因为当我们 .ic 给一个电容电压设定了初始值,仿真器会将该处节点引入强制源,等效为一个电流源并联一个很小的电导。当它直接与一个电感串联形成 LC 回路时,为了满足 IC,仿真器构造了一个“人为 DC 状态”(电感在 DC 状态下短路),这个状态在 LC/振荡器中对应一个含有巨大能量的数值等效源(等效的电流源很大)。这会导致一个“本来只是想给点初始能量”的 IC,变成了一个“巨大电流脉冲”。

总结起来,就是对于包含 LC 谐振支路的振荡器而言,这种 DC 强制过程会在电感回路中注入一笔非物理的大能量,使得本应只是设定初始状态的 IC,在数值上等效为一次巨大的电流/能量脉冲。

因此,振荡器并非通过小扰动和不稳定模态自然起振,而是被“数值方式强行踢醒”,导致初始幅度异常大、恢复时间很长,从而污染了起振过程,甚至可能影响稳态的可信度。

我们真正想要的稳态振荡是“系统属性”,它应满足:

- 起振来自极小扰动

- 振幅由非线性限幅机制决定

- 最终振荡是 limit cycle,与起始条件无关(只要不是极端)

- uic 的 IC 是靠:

-

IC 位置“选错”,也会毁掉振荡器

在这个 ECP 里:

- C2、C3、C4 属于偏置网络 / 尾电流 / 基极偏置回路,对应几十微秒量级的慢时间常数

- 真正的振荡 LC 模态在 L1 + C1,时间尺度是纳秒级

系统是“强烈多时间尺度”的。

给 C2 / C3 / C4 设 IC,本质上相当于:

- 人为注入了一大坨偏置能量,且这个能量只能通过慢路径泄放

- 数学上,激发了一个强慢模态,而这个慢模态与振荡模态弱耦合

结果就是电路先花几十微秒在“恢复偏置平衡”。在这段时间里,振荡模态被压制,最终才慢慢进入振荡。

而第二张图,选对了 IC 点位:不去碰 C2 / C3 / C4,而是:

- 用一个小幅、短时、交流扰动(在 Q2 基极加一个小阻尼正弦/小脉冲)

- 直接耦合到振荡模式

这样做的好处是:

- 激发的是正确的本征模态

- 不注入 DC 偏置能量

- 不引入慢时间常数

- 起振行为接近真实物理系统(噪声起振)

-

谐振的建立过程

一旦振荡器受到扰动,振荡就会增强,并渐近地达到其稳态振幅。如果振荡器以非常小的扰动启动,那么在增长阶段的初始部分,振荡可能会非常微弱。如果信号振幅远小于 DC,可能不足以迫使时间步长控制算法采用更小的时间步长,那么仿真器就可能无法很好地描绘初始增长阶段。甚至有可能由于时间步长过大而导致扰动的影响消失,从而使振荡器无法偏离其平衡点。需要注意的是,某些积分方法在时间步长足够大时会表现出人工数值阻尼,从而抑制振荡。为了在初始增长阶段准确预测解,有必要通过瞬态分析中的最大时间步长参数强制仿真器使用较小的时间步长。通常,最大时间步长的合理值约为预期振荡周期的二十分之一。此外,在模拟振荡器时,应考虑使用梯形法则,因为它不像 Gear2 或后向欧拉法那样表现出人工数值阻尼。在振荡器的建立阶段未强制仿真器使用较小的时间步长会导致

- 锯齿状波形

- 与开启瞬态相关的时间常数预测严重不准确

- 对振荡器首次受到扰动到其稳定下来之间延迟时间的预测极其不准确

- 该模拟器甚至可能无法预测振荡,因为

- 仿真器引入的延迟超过了瞬态分析的时间间隔

- 积分方法中的人工数值阻尼抑制了振荡

-

稳态振荡器

稳态振荡器通常在设计上是具有高 Q 值的谐振器。高 Q 值得谐振器本质上能够长时间存储能量。因此,在模拟过程中产生的误差会以非物理注入能量的形式存储在谐振器中并不断积累。对于振荡器而言,由于相位是频率的积分,所以存在一个与相位有关的无限长的时间常数。(意思就是频率是相位的微分,相位的变化本质也是频率的抖动,频率的微小抖动需要长时间对相位的积分来确定,频率抖动趋于零,积分时间趋于无穷)

因此,模拟器中的误差会导致相位漂移。此外,积分法所使用的低阶多项式会持续低估正弦波的曲率,因为正弦波具有无穷多个非零导数。这会导致系统偏差,使得相位在每一步都略微漂移,从而使频率略低。基于此,在模拟振荡器时,需要保守一点,将

reltol收紧到 0.0001。弛豫振荡器还会带来另一个难题。由于它们产生的信号具有明显的不连续性,但又不会产生断点,因此可能产生波形的拐角缺失。这种问题无法完全消除,但可以通过减小

reltol缓解,因为这有助于减小时间步长。

不稳定电路(Unstable Circuit)

不稳定的电路会给电路模拟器带来特殊的挑战。如果不额外注意,模拟器不会给出任何电路不稳定的提示。直流分析计算平衡点,但不区分稳定平衡点和不稳定平衡点。如果模拟器找到一个不稳定平衡点,除非电路受到某种干扰,它不会偏离该点,这也是为什么模拟振荡器不会自行启动,需要我们在适当的节点注入一个适当的 IC。

某些积分法还会产生人工数值阻尼,有时会导致不稳定电路的响应被计算为稳定。

考虑下面电路,正反馈使得该电路不稳定

其中 ,计算该反馈系统的传递函数(拉氏域)

该传递函数表明,正反馈不仅将 RC 引起的极点移至右半平面,还使频率提升了 A-1 倍。假如电路由一个 20 us 过渡的单位阶跃所驱动,模拟器使用 1 us 的时间步长去适应过渡区,但该步长仍然远大于 ns 的不稳定时间常数,这就是问题所在。当时间步长远大于时间常数时,积分法会产生大量人工数值阻尼,因此添加的激励无法激发出该不稳定模式。虽然梯形法不会产生人工数值阻尼,但模拟器在激励的两个拐角处都设置了断点,并且在紧接断点之后的时间步中始终使用隐式欧拉,这种隐式欧拉可能因阻尼而抑制了不稳定模式。

在断点后无法阻止模拟器使用隐式欧拉,也无法避免断点,但可以通过让模拟器采用更小的时间步长来解决这个问题。收紧 reltol 就是种简单的方法,缩短脉冲过渡时间也可以实现,还可以强制模拟器使用更小的时间步长,但这种情况下效率很低。

如果不稳定极点处于很高的频率,当仿真中用具有特别快转换时间的脉冲驱动运放,或公差异常严格,或电路出现收敛问题时,模拟器可能会采用足够小的时间步长,使得不稳定模式无法被阻尼。此时,波形会迅速飞涨至无穷大,导致瞬态分析会以一种看似模拟器收敛困难的方式失败。仔细检查计算得到的波形,特别是在仿真的最后时刻,寻找快速的指数增长。如果发现了,那么就很可能是电路中存在不稳定的极点。所以为了降低不稳定极点被忽略的可能性,建议使用快速上升时间的阶跃信号驱动电路,并以严格的容差进行仿真。

电荷储存电路(Charge-Storage Circuits)

这一块知识点总结成一句话:

当电路“靠电荷活着”时,瞬态仿真的关键不再是电压/电流精度,而是“电荷是否被正确保存”。

什么是 Charge-Storage Circuit?

凡是把信息、状态、历史“存”在电容里的电路,都是电荷存储电路。

典型例子:

- 动态存储器(DRAM、dynamic latch)

- 开关电容电路(SC、switched-capacitor)

- CCD

- 采样保持(S/H)

- 漏电极小、时间常数极长的模拟存储节点

这些电路的共同点:

- 时间常数极长

- 几乎没有耗散

- 任何微小电荷误差都会长期保留甚至累积

为什么这些电路“特别难仿”?

-

电荷误差 ≠ 电压误差

在普通模拟电路中:

- 电压/电流误差 -> 很快被 RC 衰减掉

在电荷存储电路中:

- 电荷误差不会消失

- 只会被“存下来”

-

MOSFET 的 Meyer 电容模型不守恒电荷

在普通模拟电路里:

- 误差被耗散

- 问题不明显

但在 charge-storage circuit 里:

- 每一步的 Δq

- 都会被存进电容

- 误差越滚越大

需要警惕的两点:

- 即使将时间步缩到极小,如果电容模型不守恒电荷,误差仍然会累积。

reltol≠ charge accuracy- SPICE/Spectre 主要控制的是电压 / 电流误差,但电荷不是直接控制量

- 波形“看起来很平滑、很准确”,但存储的电荷已经慢慢漂了。

工程建议:

- 必须使用 charge-conserving model

- 不要指望 Gear / 数值阻尼“帮你擦屁股”

- 收紧

reltol是“次优解”,它只能减缓,不能消除,还会拖慢仿真效率

正弦电路(Sinusoidal Circuits)

正弦波是一种特别有用的模拟测试信号,因此电路模拟器常常需要计算正弦波信号。有时它们的计算效果不佳,所以值得探讨一下问题出在哪里以及如何避免。

最常见的问题是欠采样,这个问题很容易解决,只需指定最大时间步长,以确保每个周期至少有10 到 20 个时间点即可,注意避免混叠,本质也是欠采样。

宏观模型(Macromodels)

这一块知识点总结成一句话:

即使你的积分方法、时间步控制、容差都“理论正确”,宏观模型本身也足以让瞬态仿真结果在物理意义上失真。

宏观模型遇到的核心问题是:

宏观模型(macro-model)往往为了速度和稳定性,系统性地牺牲了动态真实性,而瞬态分析是最容易“暴露这种牺牲”的地方。

什么是宏观模型(Macro-Model)?

典型例子:

- 运放宏模型(op-amp macromodel)

- 比较器宏模型

- ADC / DAC 宏模型

- 行为源(B source / Verilog-A)

- 简化的 PLL、VCO、SerDes block

它们的共同点:

- 不是器件级物理模型

- 是为了功能 + DC/AC 指标 + 仿真速度

宏观模型在瞬态分析中的“原罪”

-

为了稳定性,模型常常是非物理的

很多宏模型:

- 人为加入阻尼

- 人为限制带宽

- 人为裁剪状态变量

- 甚至引入非因果或不守恒结构

这些在DC、AC、小信号中没大问题

但在 transient 中,这些“工程修补”会直接改变动态行为

-

宏模型常常隐藏不稳定极点

前面已经铺垫过:

- 数值阻尼

- Gear

- Backward Euler

- break point 后的 BE

会把真实不稳定模态“压没”

而宏模型里常见情况是:

- 本来就有不物理的不稳定极点

- 或人为添加的“补偿极点/零点”

结果就是,看到的“稳定”,可能是 数值 + 模型 + 时间步 三重假象

-

很多宏模型不守恒能量 / 电荷

-

宏模型中:

- 常见电流源 + 受控源

- 简化电容

- 丢失内部状态

-

在 transient 中:

-

电荷悄悄产生或消失

-

能量凭空注入或耗散

-

在普通模拟电路你可能感觉不到,但在对能量 / 电荷敏感的电路中:

- 振荡器

- PLL

- charge-storage

- long-time transient

结果会完全错误

-

不要过度相信宏模型的瞬态结果,尤其在以下情况:

- 起振时间

- 抖动积累

- 锁定过程

- 微小扰动的放大

- 长时间常数行为

为什么宏模型再 transient 中看起来还能跑,结果好像还挺不错?

这是因为数值算法在起作用,帮模型兜底!例如 Gear 或隐式欧拉提供了人工数值阻尼,基于局部截断误差的时间步控制算法,断点处强制使用隐式欧拉等。这些机制会抹平振荡,压制不稳定性,掩盖模型的自身缺陷。在这些机制的共同作用下,我们会看到波形挺干净,仿真很稳定,但物理上却是不可信的。

宏模型有关的工程级建议,宏模型适合:

- 功能验证

- 大系统连通性

- DC 偏置定位

- AC 指标拟定

但不适合:

- 精确起振

- 抖动分析

- 边沿细节分析

- 能量/电荷相关现象和分析

使用宏模型跑 transient,需要强行暴露问题,方法包括使用更小的步长,用无阻尼积分法,检查是否存在非物理的能量注入。

分销网络(Distribution Networks)

在模拟电源和时钟分配网络时,人工数值阻尼可能产生显著影响。分配网络由长的电感线组成,末端连接电容。它们通常处于欠阻尼状态,而且往往欠阻尼程度相当严重。分配网络的欠阻尼特性加上流入其中的电流急剧变化会导致振铃现象。这种过度振铃可能导致整个电路出现难以捉摸的异常行为。

工程上可以认为欠阻尼振铃现象来自于阻抗不匹配,而且是太低,导致信号在源端和终端之间多次来回反射。

这种情况下,隐式欧拉或 Gear 法所表现的人工数值阻尼会抑制时钟分布网络中部分或全部振铃现象,这种人工数值阻尼相当于在电路中引入了与时间步长相关的虚假损耗元件,其表现形式更接近于给电容串联电阻或给电感并联电阻,步长越大阻尼越强。

MNA 方程中,电容的本构关系 与电阻一致,等效导纳与电阻导纳是合并在一起的,然后将历史电流源归类到右端节点电流。步长越大,等效导纳 越小,阻尼越高。电感的本构关系 需要通过电压源的未知支路电流 消元,然后带入 KCL 中,这样的话相当于为电感并联了一路阻尼,步长越大,该并联阻尼越小,分走的电流越多,电感一路电流越小阻尼越强。

由于分布网络上的偏置电平相对于振铃幅度较大较大的偏置电平会使时间步长控制算法对较小的振铃不敏感,导致仿真器相对于振铃采用较大的时间步长。因此,在模拟电感分布网络时,如果振铃是一个需要关注的问题,应避免使用含人工数值阻尼的方法,尤其是后向欧拉法,应改用梯形法。如果无法使用梯形法则,则可能需要收紧相对容差或最大时间步长,以将人工阻尼降低到可忽略的水平。

大型电路

如果电路在瞬态分析中运行得非常缓慢或停滞不前,有时可以通过查看电源电流来找到原因。仔细观察电源电流的波形,可以看到一个非常快且非常小的梯形法振铃,这就是问题所在。快速的梯形法振铃导致仿真器采取极小的时间步长,从而使其运行得非常缓慢。切换到 Gear2 可以解决此问题。

通过检查电源电流也有可能发现意外的振荡现象。如果电路本应达到平衡点之后,电源电流仍呈现出稳定的波动,那么该电路很可能包含一个振荡器。

精确电流测量

通常,电路模拟器计算电流的精度不如计算电压的精度高。

-

仿真器的“第一公民”是电压,不是电流

在 MNA 框架下:

- 未知量

- 节点电压

- 电压源 / 电感支路电流

- 非未知量

- 电容电流

- MOS 栅电流

- 大多数支路电流

这些电流是 “事后计算量”,不是直接解出来的。

- 未知量

-

大多数电流是“导数”

典型例子:

-

电容电流

-

MOS 栅电流

而瞬态分析里:

- 是用数值积分算的

- 是再做一次差分

电流 = 对数值误差做放大运算

-

-

电流误差不会被 time-step 控制很好地约束

- SPICE 的 LTE 主要控制的是状态变量

- 电容:电荷 / 电压

- 电感:磁通 / 电流

- 不是直接控制电流误差

结果导致电压看起来很平滑,电流却充满毛刺、振铃、台阶。而仿真器并不认为这是“错误”。

- SPICE 的 LTE 主要控制的是状态变量

-

电流误差不累积,因此更容易被忽略

- 电压 / 电荷误差:

- 会积累

- 会影响后续时间步

- 电流误差:

- 不积累

- 每一步“算错了就算错了”

所以电流波形可能“每个点都不准”,但整体仿真仍然完全收敛。

- 电压 / 电荷误差:

-

瞬时电流尖峰通常是数值产物,很多你看到的:

- 电容充放电尖峰

- 栅电流 spike

- 开关瞬间的大电流

并不代表真实电路,而是来源于:

- break point 后的 backward Euler

- 梯形法的点对点振铃

- 电压轨迹的不连续一阶导数

-

电流的高频内容几乎完全由数值细节决定,原因是

-

电流 = 电压的导数

-

导数在频域中:

数值噪声在高频被成倍放大。这就是为什么:

- 用 transient + FFT 看电流谱

- 往往看到“物理上不该存在的高频能量”

-

选通 / 抽样(Strobing)

Strobing 是一种“只在选定时刻采样并保存结果”的技术,用于避免高频瞬态、数值噪声和无关细节污染你真正关心的信息。

它不是数值算法,而是结果观测与数据管理方法。

为什么需要 strobing?

-

瞬态仿真“算得多,但我们不需要那么多”

在 transient 中:

- 仿真器内部:

- 可能用极小时间步

- 在 break point 附近密集求解

- 但我们关心的可能只是:

- 每个时钟沿

- 每个 UI

- 每个振荡周期的峰值

内部时间步 ≠ 你想看的时间点

- 仿真器内部:

-

“全量保存”会带来三个问题

问题 1:数据量爆炸

- 数百万个 time point

- 文件巨大

- 后处理极慢

问题 2:数值噪声被当成“物理细节”

- break point 后的 BE

- 梯形法振铃

- 数值导数误差

你看到的毛刺、尖峰、高频抖动,可能只是数值产物

问题 3:会“盯错量”

- 被瞬态细节吸引

- 忽略真正的系统行为(包络、稳态、周期性)

Strobing 的核心思想

不要试图“连续地看世界”,而是只在“有意义的时刻”看一眼。

工程化定义:

- 仿真仍然用自适应时间步、用复杂积分法

- 但只在指定时间点记录、输出、用于测量

Strobing 和“减小时间步”有什么本质区别?

| 手段 | 作用对象 | 后果 |

|---|---|---|

| 减小 maxstep | 计算过程 | 慢、但更精确 |

| tighten reltol | 误差控制 | 慢、但不一定更物理 |

| Strobing | 观察过程 | 快、且更“干净” |

典型应用场景:

- 周期性系统(振荡器 / PLL / 时钟)

- 只在每个周期同一相位,或每个上升沿,观察幅度、相位漂移、抖动

- 避免被数值振铃,高频毛刺干扰判断

- 开关电容/采样保持电路

- 对真正具有意义的状态:开关断开的瞬间

- Strobing:

- 精确抓住这些时刻

- 避免在导通阶段读取垃圾电流/电压

- 长时间 transient(慢动态 + 快动态并存)

- 例如偏置慢恢复()+ 高频振荡()

- Strobing 允许只看时间尺度上的离散快照,而不是被 GHz 波形淹没

很多看起来异常的瞬态细节,在 strobe 采样后会自然消失,这可能是高频非相干数值噪声导致的,Strobing 等价于低通/相干采样,会滤除这部分异常。

总结

瞬态分析不是“电路行为的客观重放”,而是“电路 + 数值方法 + 模型 + 误差控制”的共同产物。

也就是说,仿真结果既不完全等于物理现实,也不完全等于数值误差,而是二者的耦合。

凝练几个核心判断

-

数值稳定 ≠ 物理稳定

- Gear / Backward Euler -> 保证数值稳定

- 但可能掩盖振荡、掩盖不稳定极点、改变起振行为

仿真“跑得稳”,并不代表电路“本来就稳”

-

时间步是隐含电路参数

- 时间步并不是一个“纯数值参数”,而是在瞬态分析中等效为电路的一部分

- 时间步过大,等效引入阻尼,等效改变极点;时间步过小,放大模型/电流噪声,仿真的时间和算力成本爆炸

maxstep、LTE、reltol不是“仿真设置”,而是“隐含模型”

-

瞬态误差控制主要针对“状态变量”,不是看到的所有量

- LTE 控制的是电容电荷、电感磁通、节点电压,而非瞬时电流、导数、高频细节

- 看起来很平滑的波形,不等于被严格控制过误差的波形

-

模型质量比积分方法更重要

- 再好的数值方法,也救不了错误或不诚实的模型,尤其是

- 不守恒电荷的模型

- 过度简化的宏模型

- 认为裁剪动态的行为源

- 瞬态分析中,模型缺陷的影响远大于数值方法选择

- 再好的数值方法,也救不了错误或不诚实的模型,尤其是

-

初始条件和激励方式会“决定你看到哪个物理过程”

不同的 IC 设置,例如

- UIC / non-UIC

- node IC / branch IC

- 强制 DC / 小扰动源

决定激发的是哪一个模态(快/慢/非物理)

-

看结果的方式和算结果同样重要

如果不知道该在什么时候、以什么方式观察结果,那看到的很可能只是数值噪声。所以

- Strobing

- 平均量

- 周期采样

- 积分量

是瞬态分析不可分割的一部分

可以长期用的判断准则:

- 仿真稳定,不等于电路稳定

- 时间步是隐藏的电路参数

- 积分法决定你“能不能看到”某些物理现象

- 模型错误,比数值误差更致命

- 瞬态仿真最常见的失败,不是算错,而是误读